RAM RHEA compiler IP

Filter

Compare

255

IP

from

80

vendors

(1

-

10)

-

TSMC CLN7FF Synchronous One Port Register File Compiler

- High Current One Port Register File operates within a voltage range from 0.675 V to 0.825 V and a junction temperature range from -40 oC to 125 oC. The available supported macro size is configured from 144 bits to 72K bits. The Compiler is divided into 3 groups according to their column-selected numbers (Mux=1, 2 or 4).

- Pins and metal layers

- Compilation option

- Power management

-

Single Port SRAM compiler - Memory optimized for high density and low power - Dual Voltage - compiler range up to 320 k

- REACH THE HIGHEST DENSITY

- Thanks to smart periphery design

- Typically up to 20% gain in density versus alternative HD-LP RAM depending on instance configuration

- Using Pushed Rules Foundry bitcell

-

Single Port SRAM compiler - Memory optimized for high density and low power - Deep N Well supported - compiler range up to 320 k

- REACH THE HIGHEST DENSITY

- Thanks to smart periphery design

- Typically up to 20% gain in density versus alternative HD-LP RAM depending on instance configuration

- Using Pushed Rules Foundry bitcell

-

Foundry sponsored - Single Port SRAM compiler - Memory optimized for high density and low power - Dual Voltage - compiler range up to 320 k

- FOUNDRY SPONSORED

- HIGHEST DENSITY

- -Smart periphery design

- -Typically up to 20% gain in density versus alternative HD-LP RAM depending on instance configuration

-

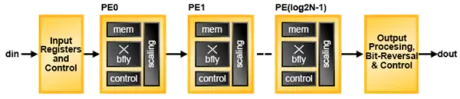

FFT Compiler

- Wide range of points sizes: 64, 128, 256, 512, 1024, 2048, 4096, 8192, and 16384

- Choice of high-performance (streaming I/O) and low resource (burst I/O) versions

- Run-time variable FFT point size

- Forward, inverse or port-configurable forward/inverse transform modes

-

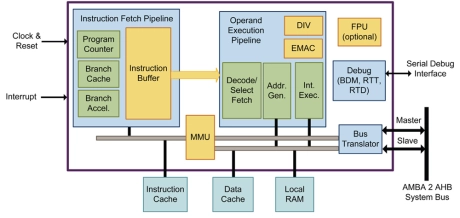

ColdFire V4 Processor delivering 500 DMIPS of performance

- The ColdFire V2 Core & Standard Product Platform (CFV2SPPC1) combines the ColdFire V2 Core with industry-proven platform peripherals to form a complete low-cost, low-power microcontroller subsystem supported by a vast ecosystem of development tools and runtime software.

- The CFV2SPPC1 is the same ColdFire V2 processor core and platform/peripheral IP implemented in NXP MCF5208 devices.

-

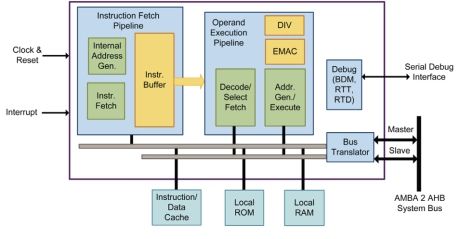

ColdFire V2 IP Core low-gate count, high performance ColdFire architecture

- Variable-length RISC, clock-multiplied core

- 166-MHz in typical 130-nm process

- Independent, decoupled pipelines: 2-stage instruction fetch pipeline (IFP); 2-stage operand execution pipeline (OEP); FIFO instruction buffer is the decoupling mechanism

- 16 user-accessible, 32-bit general purpose registers (GPRs)

-

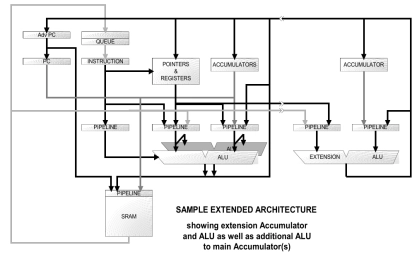

Application Adaptive Processor

- High Performance

- Multi-cycle, Single cycle and Superscalar variants

- 16-bit expandable Instruction Set

- 16-bit, 32-bit and 64-bit versions

-

6809 compatible 8-bit microprocessor

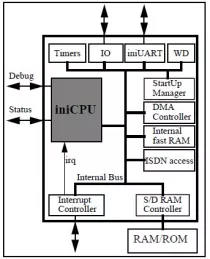

- iniCPU, a powerful 8-bit micro processor, enables embedded computing and controlling on chip. It fulfils all needed requirements for being used in systems on chip and high level programming.

- Although existing standard products are cheap today, there are a lot of applications where an integration of the micro processor brings total system cost down.

- Less components, higher performance, glueless memory interfaces and customized peripherals allow you to build your system on chip.