QSPI IP

Filter

Compare

30

IP

from

12

vendors

(1

-

10)

-

QSPI Master IP

- The QSPI master core is easy to use, simple to work with, quick to operate, and reliable under all conditions.

- It supports the majority of QSPI devices standard from a standard AXI4 slave interface. It also features support for Octal SPI, Dual SPI (DSPI), and SPI interface.

-

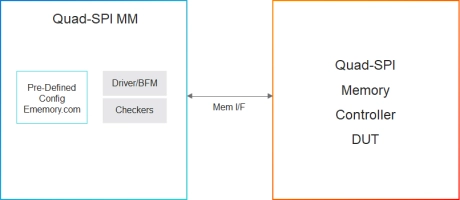

Simulation VIP for Q-SPI

- Device Density

- From 256Mb to 2Gb with frequency up to 166MHz

- Operation Mode

- Single I/O, Dual I/O, and Quad I/O (Q-SPI and QSPI) with single and double transfer rate (STR and DTR)

-

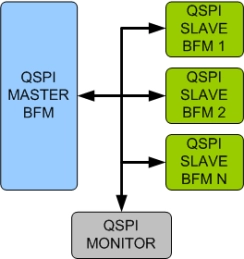

QSPI (Quad Serial Peripheral Interface) Verification IP

- Supports Master and Slave Mode

- Supports the following modes in Serial Peripheral Interface

- Mode 0

- Mode 3

-

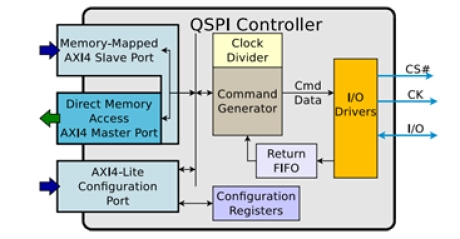

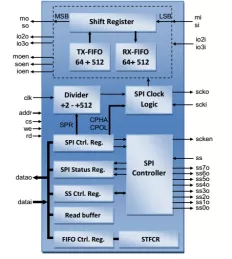

Quad SPI Controller

- The SPI controller support master/slave operation over the single-lane, dual-lane,quad-lane and half duplex singlelane protocols

- Programmable clock polarity and phase (CPOL/CPHA)

- Configurable MSB First or LSB First

- Master/Slave mode configurable frequency (FPCLK/2 max)

- SPI bus busy status flag

-

QSPI FLASH Controller – XIP functionality (SINGLE, DUAL and QUAD SPI Bus Controller with Double Data Rate support)

- Set of software accessible control registers to execute any Flash memory command

- Supports any device clock frequency, polarity and phase,

- Programmable baud rate generator,

- Built in FLASH Commands decoder supports most popular FLASH devices,

-

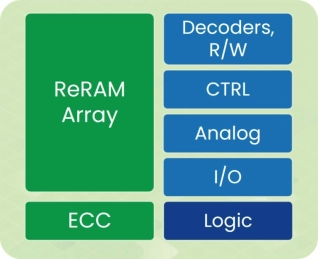

ReRAM NVM in DB HiTek 130nm BCD

- 10K cycles endurance

- >10 years retention at 125°C

- Ultra-low power consumption

- Low-cost NVM – requires only two additional masks

-

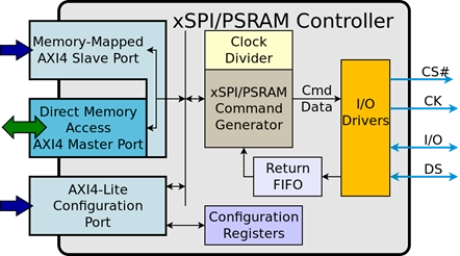

xSPI - PSRAM Master

- The xSPI/PSRAM master IP is easy to use, simple to work with, quick to operate, and reliable under all conditions. It supports the xSPI JESD~251 standard from a standard AXI3 or AXI4 slave interface.

- It also supports APMemory Octal/QSPI RAM, HyperRAM, HyperFlash, and features backwards compatibility support for Octal SPI, QSPI, DSPI, and SPI interfaces.

-

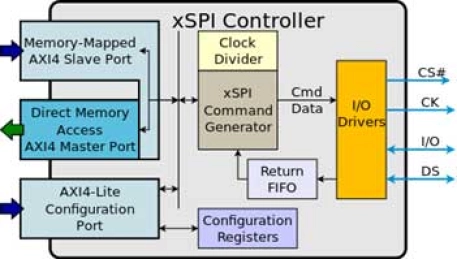

xSPI Master IP | NOR IP

This Universal NOR Flash IP supports a variety of NOR Devices and multiple Protocols, combines ease of use with high reliability, low power and speed under all conditions, including automotive applications.

The xSPI master IP supports the xSPI JESD251 standard from a standard AXI4 slave interface, and also features backwards compatibility support for Octal SPI, QSPI, DSPI, and SPI interfaces. Also supports JEDEC SFDP Standard.

-

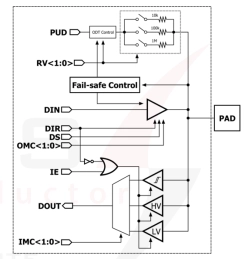

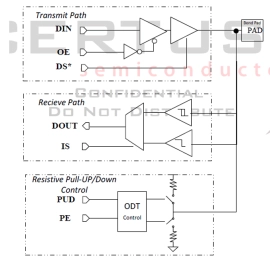

1.8V/3.3V Multi-Voltage GPIO in TSMC 28nm

- This silicon-proven TSMC 28nm Digital I/O Library delivers a high-performance, low-power interface solution designed for advanced digital applications.

- Featuring a triple-staggered architecture, this versatile library supports multi-voltage and multi-protocol GPIO, ensuring seamless integration across diverse system requirements.

-