PSRAM Controller IP

Filter

Compare

17

IP

from

14

vendors

(1

-

10)

-

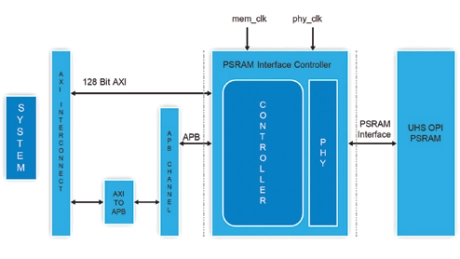

AP Memory UHS PSRAM Controller

- This controller supports AP Memory’s UHS series of high speed PSRAM devices which can clock frequencies of upto 1066 MHz.

- This controller enables smooth integration of APMemory’s UHS OPI PSRAM memory device chips into various new-gen devices made with mobile and wearable low power SoCs’.

- This memory controller implementation is designed to give the user full flexibility for driving the memory control signals and timing adjustment for data sampling.

-

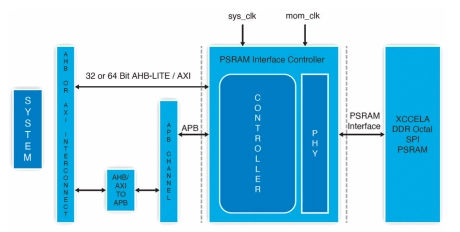

Octal SPI DDR PSRAM controller

- This controller supports AP Memory’s Xccela open standard Bus for digital interconnect and data communications, suitable for non-volatile and volatile memories such as PSRAM.

- This controller enables smooth integration AP memory’s of Xccela PSRAM memory chips into various new-gen devices made with mobile and wearable low power SoCs’.

- This memory controller implementation is designed to give the user full flexibility for driving the memory control signals and timing adjustment for data sampling.

-

PSRAM Memory Controller IP

- DFSPI – SPI FLASH Controller with Execute in place – XIP (SINGLE, DUAL and QUAD SPI Bus Controller with DDR / DTR support and optional AES Encryption) + … NOR & NAND Flash Memory Support

-

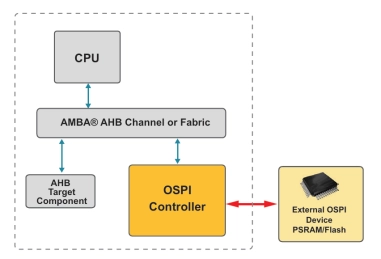

AHB Octal SPI Controller with PSRAM and XIP Support

- The Octal SPI Memory Controller IP core is a serial peripheral interface (SPI) master which controls an external serial device, usually an industry-standard FLASH or PSRAM memory device.

- In Software Mode, an AHB Master may access the register interface of the Controller to implement a wide range of protocol variants and/or commands on the SPI bus.

-

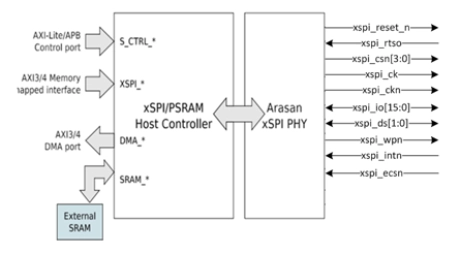

16-Bit xSPI PSRAM PHY

- Supports for both the xSPI and PSRAM Master host controller IPs.

- Support 500Mbps per line along with the high speed xSPI modes > 50MHz.

-

PHY IO for PSRAM memory PHY, 1066Mbps on TSMC 22nm

- The PHYIOs is used to transfer the Command/Address/Clk and Data between the memory controller PHY and the PSRAM device

- The TX is designed to send information from PHY to PSRAM and RX is designed to receive information which is from PSRAM

- there are bi-direction DQ IO, TX-only CK IO, filler cell with differrent size and VDDQ/VSS power clamp IO included in the PHYIOs.

-

General Memory Controller

- The GMC (General Memory Controller) includes two memory controllers: The NOR/PSRAM memory controller, The Synchronous DRAM (SDRAM/Mobile LPSDR SDRAM) controller

-

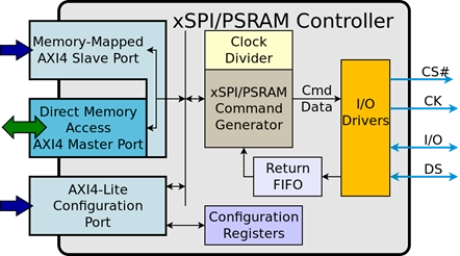

xSPI - PSRAM Master

- The xSPI/PSRAM master IP is easy to use, simple to work with, quick to operate, and reliable under all conditions. It supports the xSPI JESD~251 standard from a standard AXI3 or AXI4 slave interface.

- It also supports APMemory Octal/QSPI RAM, HyperRAM, HyperFlash, and features backwards compatibility support for Octal SPI, QSPI, DSPI, and SPI interfaces.

-

xSPI Multiple Bus Memory Controller

- SLL’s unified xSPI Multiple Bus Memory Controller IP supports the widest range of JEDEC xSPI and xSPI-like NOR Flash and PSRAM memories (JEDEC xSPI Profile 1.0 and 2.0, HyperBus 1.0, 2.0 and 3.0, OctaBus and Xccela Bus) that are available now from many memory vendors.

- JEDEC xSPI and xSPI-like memories offer good performance with lower hardware and power costs. Memory device variants offer up to 512 Mbit PSRAM, up to 2 Gigabit NOR Flash, up to 250 MHz DDR clock speeds, with x4, x8 and x16 data path widths, and a wide range of package options including 4mm x 4mm BGA49 and tiny WLCSP footprints. Some PRSAM devices are now also available with internal ECC.

-

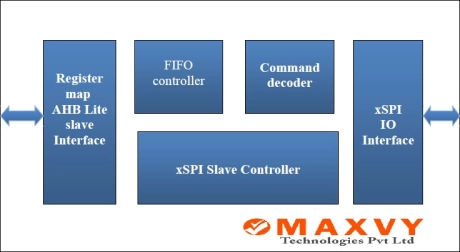

Expanded Serial Peripheral Interface (xSPI) Slave Controller

- The JESD251 Expanded Serial Peripheral Interface Slave controller is provides high data throughput, low signal count, and limited backward compatibility with legacy Serial Peripheral Interface(SPI) devices

- It is used to connect xSPI Master devices in computing, automotive, Internet of Things, Embedded system and mobile system processor to non-volatile memories, graphics peripherals, networking peripherals,FPGAs, sensors devices