PAM4 Serdes IP

Filter

Compare

35

IP

from

14

vendors

(1

-

10)

-

100G SerDes PAM4 PHY

- The SERDES PHY IP delivers a high-performance, low-power solution for high-speed interfaces up to 112Gbps.

- It supports diverse applications including AI accelerators, data centers, 5G infrastructure, and automotive SoCs.

-

112G-ULR PAM4 SerDes PHY

- Supports full-duplex 1.25Gbps to 112.5Gbps data rates

- Superior bit error rate (BER) performance across high-loss and reflective channels

- Compliant with IEEE 802.3ck and OIF standard electrical specifications

- Supports flexible SoC floorplan and IP placement and provides package substrate guideline/reference designs

-

112G-ELR PAM4 SerDes PHY - TSMC 5nm

- TSMC 5nm FinFET CMOS Process

- Power-optimized for ELR and LR links

- Integrated BIST capable of producing and checking PRBS

- 56-112Gbps PAM4 or 1-56Gbps NRZ data rates

-

56G-LR Pam4 SerDes PHY

- Supports Ethernet, FC, CPRI, and eCPRI protocols

- Compliant to IEEE 802.3ck and OIF standard electrical specifications

- Supports 56Gbps PAM4 and 28G, 10G, and sub-10Gbps NRZ data rates

- Unique firmware-controlled adaptive power design provides optimal power and performance tradeoffs and more efficient system designs based on platform requirements

- Continuous calibration and adaption provide robust performance across process, voltage, and temperature

- Supports industrial temperature range -40°C – 125°C

-

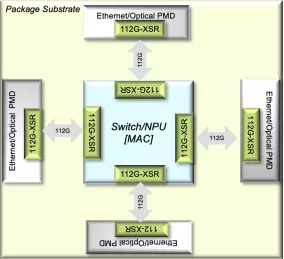

112G-VSR PAM4 SerDes PHY - PPA optimized for short reach connectivity

- 1.25Gbps to 116Gbps flexible data rates allowing simultaneous support of different protocols including Ethernet and OTN

- Power optimized for short-reach applications with configurability

- Superior bit error rate (BER) with extra performance margin beyond short-reach standard requirements

- Beachfront optimized floorplan allows north-south and east-west SoC edge placement

- Comprehensive on-chip diagnostic features make system testing and debugging quick and easy

- Enables 800Gbps networking with PHY and Controller solutions

-

1-56Gbps Serdes - 7nm (Multi-reference Clock)

- The innovative architecture utilizing advanced DSP techniques demonstrated excellent scalability over data rates and insertion losses, superior reliability, and extreme CDR robustness over a wide range of PVT.

-

1-56Gbps Serdes - 7nm (Ultra Low Latency)

- The innovative architecture utilizing advanced DSP techniques demonstrated excellent scalability over data rates and insertion losses, superior reliability, and extreme CDR robustness over a wide range of PVT.

-

1-56Gbps Serdes - 7nm (Area-optimized)

- The innovative architecture utilizing advanced DSP techniques demonstrated excellent scalability over data rates and insertion losses, superior reliability, and extreme CDR robustness over a wide range of PVT.

-

1-112Gbps Serdes - 7nm

- The innovative architecture utilizing advanced DSP techniques demonstrated excellent scalability over data rates and insertion losses, superior reliability, and extreme CDR robustness over a wide range of PVT.

-

1-56Gbps Serdes - 7nm (PPA-optimized)

- The innovative architecture utilizing advanced DSP techniques demonstrated excellent scalability over data rates and insertion losses, superior reliability, and extreme CDR robustness over a wide range of PVT.