Nios II IP

Filter

Compare

26

IP

from

5

vendors

(1

-

10)

-

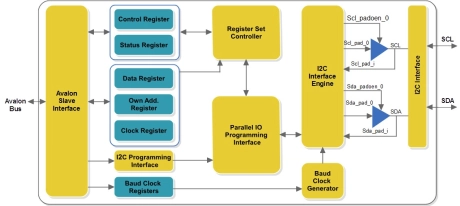

I2C Master

- Avalon compliant I²C Master IP core provides an interface between Nios II processor and an I²C Slave device.

- It can work as a master transmitter or master receiver depending on working mode determined by Nios II processor.

- The I²C Master IP core incorporates all features required by the latest I²C specification including clock synchronization, arbitration, multi-master systems and fast-speed transmission mode.

-

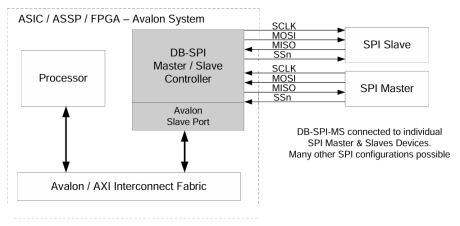

SPI Controller IP- Master/ Slave, Parameterized FIFO, Avalon Bus

- The Digital Blocks DB-SPI-MS-AVLN is a Serial Peripheral Interface (SPI) Controller Verilog IP Core supporting both Master/Slave SPI Bus transfers.

- The DB-SPI-MS contains an Avalon Bus Interface for interfacing a microprocessor to external SPI Master/Slave devices.

-

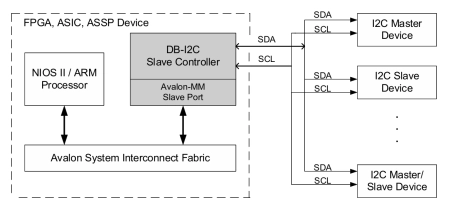

I2C Controller IP – Slave, Parameterized FIFO, Avalon Bus

- The DB-I2C-S-AHB Controller IP Core interfaces a NIOS II, ARM, MIPS, PowerPC, ARC or other high-performance microprocessor via the Avalon System Interconnect Fabric to an I2C Bus.

- The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices.

-

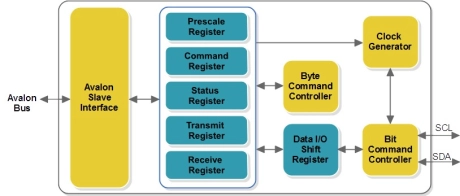

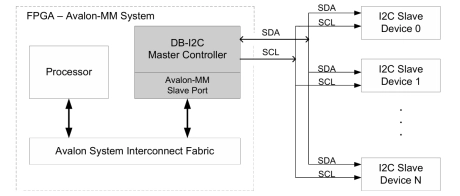

I2C Controller IP – Master, Parameterized FIFO, Avalon Bus

- The DB-I2C-M-AVLN Controller IP Core interfaces a microprocessor via the Avalon Bus to an I2C Bus. The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices, typically with a microprocessor behind the master controller and one or more slave devices.

- The DB-I2C-M-AVLN is a Master I2C Controller that controls the Transmit or Receive of data to or from slave I2C devices. In an Altera FPGA, typically, the microprocessor is a NIOS II processor, but can be any FPGA embedded processor. Figure 1 depicts the system view of the DB-I2C-M-AVLN Controller IP Core embedded within an FPGA integrated circuit device.

-

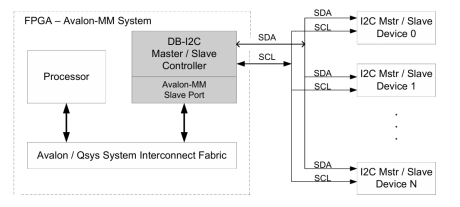

I2C Controller IP- Master / Slave, Parameterized FIFO, Avalon Bus

- The DB-I2C-MS-AVLN Controller IP Core interfaces a microprocessor via the Avalon Bus to an I2C Bus in Standard-Mode (100 Kbit/s) / Fast-Mode (400 Kbit/s) / Fast-Mode Plus (1 Mbit/s) / Hs-Mode (3.4+ Mb/s) / Ultra Fast-Mode (5 mbit/s).

- The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices, typically with a microprocessor behind the master controller and one or more slave devices.

- The DB-I2C-MS-AVLN is a Master / Slave I2C Controller that in Master Mode controls the Transmit or Receive of data to or from slave I2C devices while in Slave Mode allows an external I2C Master device to control the Transmit or Receive of data.

-

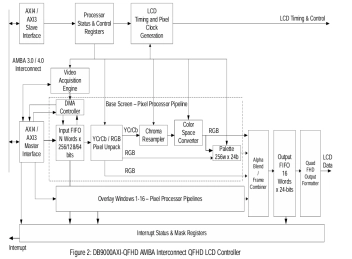

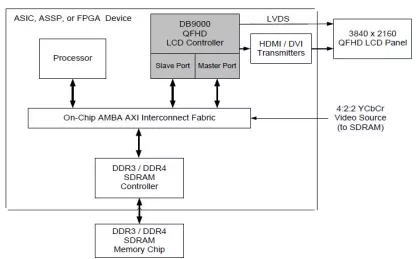

Display Controller – Ultra HD LCD / OLED Panels (AXI4/AXI Bus)

- The DB9000AXI4-UHD LCD Controller IP Core interfaces a video image in frame buffer memory via the AMBA 3.0 / 4.0 AXI Protocol Interconnect to an 4K/8K TFT LCD / OLED display panel.

- The video image in frame buffer memory can be 8/10/12-bit 4:2:0 or 4:2:2 or 4:4:4 sampled YCrCb video or 4:4:4 RGB. For 4:2:0 and 4:2:2 YCrCb, the chroma components are re-sampled to 4:4:4 and color converted to RGB.

-

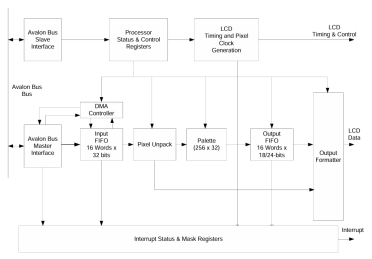

Display Controller – LCD / OLED Panels (Avalon Bus)

- The DB9000AVLN TFT LCD Controller IP Core interfaces a microprocessor and frame buffer memory via the Avalon Bus within Altera Qsys Integration (generating the System Interconnect Fabric) to a TFT LCD panel.

- In an Altera FPGA, typically, the microprocessor is a NIOS II or ARM processor and frame buffer memory is either on-chip SRAM memory or larger off-chip SRAM or SDRAM.

-

Display Controller – 4K Digital Cinema LCD Panels (AXI4/AXI Bus)

- The DB9000AXI-DCI LCD Controller IP Core interfaces a video image in frame buffer memory via the AMBA 3.0 / 4.0 AXI Protocol Interconnect to a 4K and 2K Digital Cinema Initiative (DCI) High Definition TFT LCD panel

- The video image in frame buffer memory can be 8/10/12-bit YCrCb or RGB, with a Color Space Convert to match the source video to the TFT LCD panel requirements

-

I2C Controller

- I²C (Inter-Integrated Circuit) Controller is a two-wire, bi-directional serial bus that provides simple and efficient method of data transmission over a short distance between many devices.

- Avalon compliant I²C Controller provides an interface between Nios II processor and I²C device.

- It can work as Master/Slave transmitter or Master/Slave receiver depending on working mode determined by Nios II processor.