Memory 22FDX IP

Filter

Compare

12

IP

from

5

vendors

(1

-

10)

-

Single Port High-Speed Multi Bank SRAM Memory Compiler on GF 22FDX+

- Ultra-Low Leakage - GLOBALFOUNDRIES low-leakage 6T L110 bit cells with High Vt and low leakage periphery to ensure minimal leakage and high yield.

- Multi-Bank Architecture - Memory split into 1 to 4 banks for reduced bit line length and enhanced timing.

- Ultra Low Power Standby - Built-in source biasing trims standby current to a minimum for data retention.

-

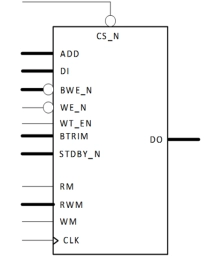

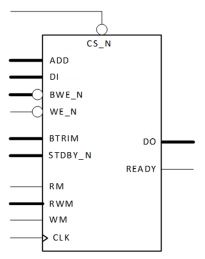

Single Port Low Leakage SRAM Memory Compiler on GF 22FDX+

- Ultra-Low Leakage: High VT (HVT) and low leakage (LLHVT) devices are used with source biasing to minimize standby currents while operating at low voltage

- Bit Cell: Utilizes GlobalFoundries® Ultra-Low Leakage, 6T(L110) bit cells to ensure high manufacturing yields

- Five Power Modes: High Performance, Low Leakage, Standby, Retention, and Power Off modes provide flexibility for power optimization

-

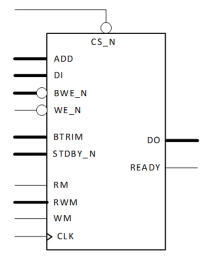

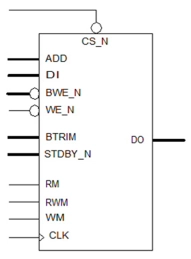

Single Port Low Leakage SRAM Memory Compiler on GF 22FDX+

- Ultra-Low Leakage: High VT (HVT) and low leakage (LLHVT) devices are used with source biasing to minimize standby currents while operating at low voltage

- Bit Cell: Utilizes GlobalFoundries® Ultra-Low Leakage 6T (P110UL) bit cells to ensure high manufacturing yields

- Five Power Modes: High Performance, Low Leakage, Standby, Retention, and Power Off modes provide flexibility for power optimization

- Speed Grades: Three options to adjust the speed/leakage balance and optimize for high speed or low power operation

-

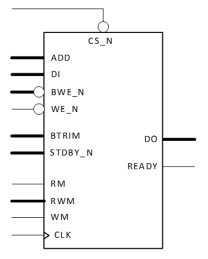

Single Port Low Leakage SRAM Memory Compiler on GF 22FDX

- Ultra-Low Leakage: High VT (HVT) and low leakage (LLHVT) devices are used with source biasing to minimize standby currents while operating at low voltage

- Bit Cell: Utilizes GlobalFoundries® Ultra-Low Leakage 6T (P110UL) bit cells to ensure high manufacturing yields

- Five Power Modes: High Performance, Low Leakage, Standby, Retention, and Power Off modes provide flexibility for power optimization

- Speed Grades: Three options to adjust the speed/leakage balance and optimize for high speed or low power operation

-

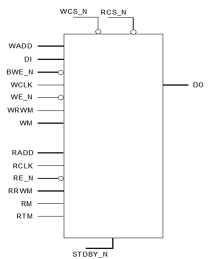

Dual Port Register File Compiler (1 Read-only port, 1 Write-only port) - GF 22FDX+

- Uses 8T-TP185SL bit cells.

- Isolated Supplies: Periphery and array power domains can be independently powered down in standby mode.

- Deep Sleep Standby Mode: Memory retains data at minimal power via internal biasing.

-

Single Port Low Leakage Register File Compiler - GF 22FDX+

- Ultra-Low Leakage: High VT (HVT) and low leakage HVT (LLHVT) devices used with source biasing to minimize standby currents while operating at low voltage.

- Bit Cell: Utilizes GlobalFoundries® Ultra-Low Leakage 6T (L110) bit cells to ensure high manufacturing yields.

- Four Power Modes: Active, Standby, Retention, and Power Off modes provide flexibility for power optimization

-

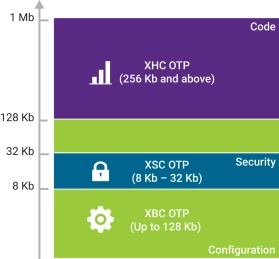

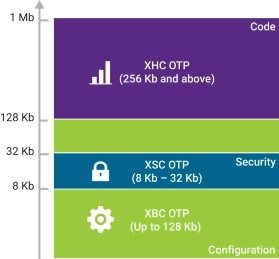

GF 22FDX 5.5V OTP Auto-Grade1 IO Staggered

- Designers face the challenge of creating secure, cost-effective, low power, and reliable SoC designs

- Synopsys’ embedded one-time programmable (OTP) non-volatile memory (NVM) IP, based on XHF architecture, enables designers to address these challenges

- Synopsys’ OTP NVM IP architecture provides high levels of security, high yields, low power, and excellent reliability, which is why Synopsys OTP NVM is the leader in antifuse technology with >10B units shipped and availability in more than a dozen foundries

- Synopsys OTP NVM IP is silicon-verified in TSMC N4P, N5, N5A, N6, and N7

-

GF 22FDX 5.5V OTP Auto-Grade1 IO Inline

- Designers face the challenge of creating secure, cost-effective, low power, and reliable SoC designs

- Synopsys’ embedded one-time programmable (OTP) non-volatile memory (NVM) IP, based on XHF architecture, enables designers to address these challenges

- Synopsys’ OTP NVM IP architecture provides high levels of security, high yields, low power, and excellent reliability, which is why Synopsys OTP NVM is the leader in antifuse technology with >10B units shipped and availability in more than a dozen foundries

- Synopsys OTP NVM IP is silicon-verified in TSMC N4P, N5, N5A, N6, and N7

-

Single Rail SRAM GLOBALFOUNDRIES 22FDX

- Ultra-low voltage logic designs using adaptive body biasing demand dense SRAM solutions which fully integrate in the ABB aware implementation and sign-off flow of the Racyics® ABX Platform solution.

- The Racyics® Single Rail SRAM supports ultra-low voltage operation down to 0.55 V where logic designs with Minimum-Energy-Point are implemented.

-

Dual Rail SRAM Globalfoundries 22FDX

- Single port SRAM compiler based on P124 bitcell with Dual-supply-rail architecture

- Bitcell array supply voltage 0.8V and ULV core interface down to 0.4V enabled with Racyics' ABB