MIPI DSI Receiver IP

Filter

Compare

25

IP

from

11

vendors

(1

-

10)

-

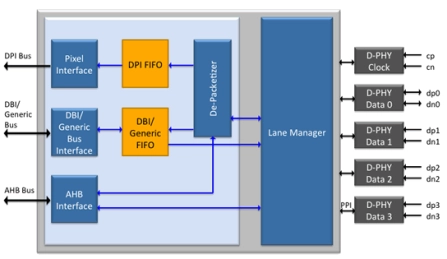

DSI Receiver Controller

- The DSI v1.3 Receiver Controller IP is designed to provide MIPI DSI 1.3 compliant high-speed serial connectivity for device (mobile display modules) with Type 1 to 4 architectures.

- Serial connectivity to the mobile applications processor’s DSI host is implemented using 1 to 4 D-PHY’s (also available from Arasan), depending on display bandwidth needs.

-

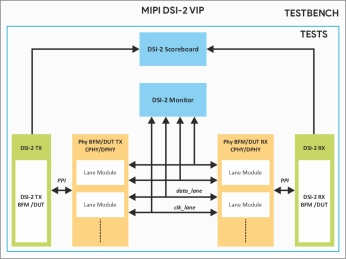

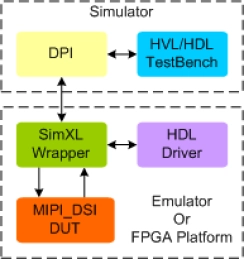

MIPI DSI v2.2 Verification IP

- Compliant to MIPI DSI Specification version 2.2 and MIPI C-PHY Specification version 2.1 with PPI interface.

- Support all Calibration Format & operations

- C-PHY supports MFAA and SFAA for DSI TX and RX respectively for Data Lane Module in command mode.

- C-PHY supports MFAN and SFAN for DSI TX and RX respectively for data Lane Module in video mode.

-

MIPI DSI v1.3.2 Verification IP

- Compliant to MIPI DSI Specification version 1.3.2 and MIPI D-PHY Specification version 1.2 with PPI interface.

- Support all Calibration Formats & operations

- D-PHY supports MFAA and SFAA for DSI TX and RX respectively for Data Lane Module in command mode.

- D-PHY supports MFAN and SFAN for DSI TX and RX respectively for Data Lane Module in video mode.

-

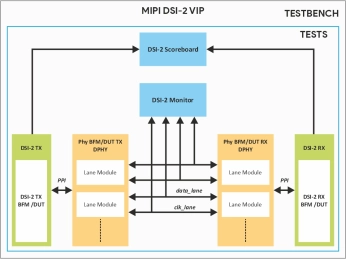

MIPI DSI Verification IP

- Full MIPI DSI Transmitter and Receiver functionality.

- Supports 1.3.1 MIPI DSI/2.0 MIPI DSI-2 Specifications.

- Supports PPI interface.

- Operates as a Transmitter, Receiver, or both.

-

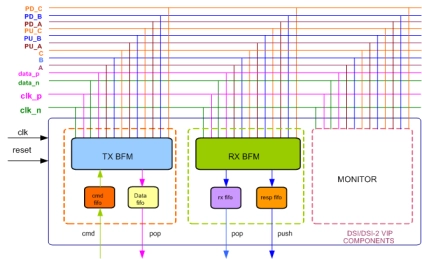

MIPI DSI Synthesizable Transactor

- Full MIPI DSI Transmitter and Receiver functionality.

- Supports MIPI DSI v1.3 and MIPI DSI-2 v1.1 Specifications.

- Supports PPI interface.

- Operates as a Transmitter, Receiver, or both.

-

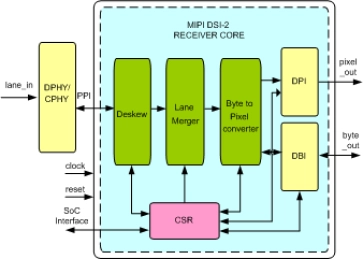

MIPI DSI-2 Receiver IIP

- Compliant with MIPI DSI-2 specification v1.3

- Compliant with D - PHY Specification v1.1,v1.2,v2.0,v2.1

- Compliant with C - PHY Specification v0.7,v1.2

- Compliant with Display Pixel Interface (DPI -2) v 2.0

-

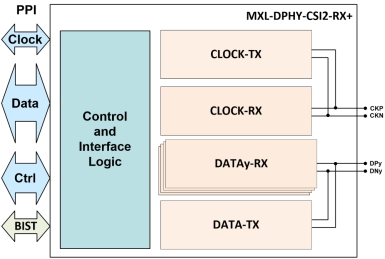

MIPI D-PHY RX+ (Receiver) IP

- The MIPI® D-PHY RX+ is a proprietary implementation of the MIPI Camera Serial Interface 2 (CSI-2) and Display Serial Interface (DSI) D-PHY Receiver.

- It is optimized to achieve full-speed production testing, in-system testing, and higher performance compared to traditional configurations, while reducing area and standby power.

-

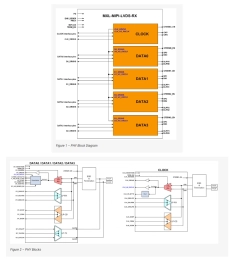

MIPI D-PHY/LVDS Combo Receiver IP

- The MXL-LVDS-MIPI-RX is a high-frequency, low-power, low-cost, source-synchronous, Physical Layer that supports the MIPI® Alliance Standard for D-PHY and compatible with the TIA/EIA-644 LVDS standard.

- The IP is configured as a MIPI slave and consists of 5 lanes: 1 Clock lane and 4 data lanes, which make it suitable for display serial interface applications (DSI).

-

MIPI D-PHY TX & RX + DSI & CSI Controllers

- Compliant with MIPI Committee Specifications

- High Data Rates: Supports data transmission rates up to 4.5Gbps per lane, allowing for high-resolution displays and smooth refresh rates

- Energy Efficiency: Optimized for low power consumption, making it ideal for battery-powered devices

- Complete Display Solution: Combines the MIPI D-PHY Transmitter PHY and DSI Controller to make it a one-stop solution

-

MIPI CD PHY Combo TX & RX + DSI & CSI Controller

- Our MIPI CD-PHY Transmitter and receiver PHY with Display Serial Interface (DSI) and Camera Serial Interface (CSI) Controllers are tailored for high-performance display and camera interface applications.

- These two PHY (TX and RX) integrated systems ensure seamless communication between the processor and display, the processor and camera; supporting high data rates and efficient power consumption.