MIPI D-PHY v2.5 IP

Filter

Compare

31

IP

from

6

vendors

(1

-

10)

-

MIPI C-PHY v2.0 /D-PHY v2.5 Combo IP in TSMC

- Compliant with MIPI D-PHY spec up to v2.5 and C-PHY spec up to v2.0

- Support both MIPI DSI and CSI-2 protocols

-

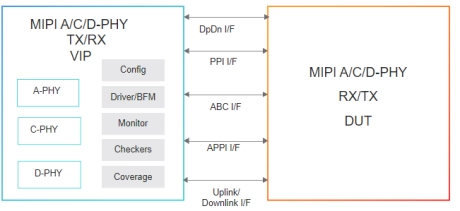

Simulation VIP for MIPI D-PHY, C-PHY and A-PHY

- PHY Monitor

- Built-in scoreboarding between serial/PPI interface, also monitors error signal interface

- Reports any detected error on any lane on serial interface and is not reflected on PPI interface

- C-PHY and D-PHY

-

MIPI D-PHY

- Compliant with the MIPI D-PHY spec v2.5

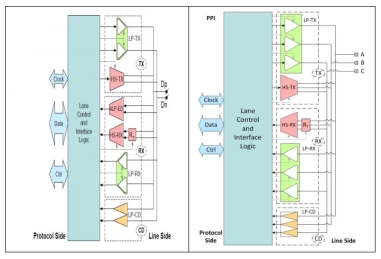

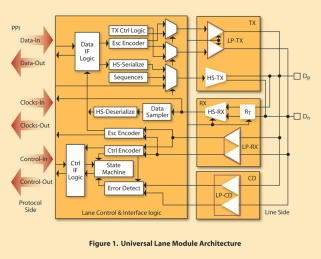

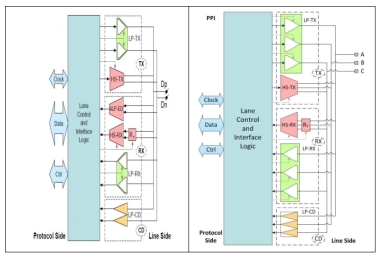

- Fully integrated hard macro with lane control and interface logic

- Up to 1.5 Gbps per lane with upgradable option to 2.5 Gbps per lane

- Supports PHY Protocol Interface (PPI)

- Low-power escape modes and ultra low-power state modes

-

MIPI D-PHY Rx IP, Silicon Proven in TSMC 12FFC

- Compliant with MIPI D-PHY spec up to v2.5 and C-PHY spec up to v2.0

- Support both MIPI DSI and CSI-2 protocols

- Support HS data rate up to 6Gbps ( 6Gsps ) per lane (per trio)

- Support LS data rate of 10Mbps and Ultra-low power mode

-

MIPI D-PHY Tx IP, Silicon Proven in TSMC 12FFC

- Compliant with MIPI D-PHY spec up to v2.5 and C-PHY spec up to v2.0

- Support both MIPI DSI and CSI-2 protocols

- Support HS data rate up to 6Gbps ( 6Gsps ) per lane (per trio)

- Support LS data rate of 10Mbps and Ultra-low power mode

-

MIPI D-PHY Rx IP, Silicon Proven in TSMC 7FF

- Compliant with MIPI D-PHY spec up to v2.5 and C-PHY spec up to v2.0

- Support both MIPI DSI and CSI-2 protocols

- Support HS data rate up to 6Gbps ( 6Gsps ) per lane (per trio)

- Support LS data rate of 10Mbps and Ultra-low power mode

-

MIPI D-PHY Tx IP, Silicon Proven in TSMC 7FF

- Compliant with MIPI D-PHY spec up to v2.5 and C-PHY spec up to v2.0

- Support both MIPI DSI and CSI-2 protocols

- Support HS data rate up to 6Gbps ( 6Gsps ) per lane (per trio)

- Support LS data rate of 10Mbps and Ultra-low power mode

-

MIPI D-PHY IP

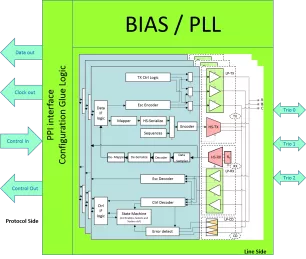

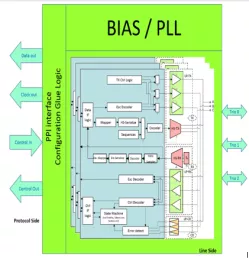

- The D-PHY is partitioned into a Digital Module – CIL (Control and Interface Logic) and a Mixed Signal Module. It is provided as a combination of Soft IP views (RTL, and STA Constraints) for Digital Module, and Hard IP views (GDSII/CDL/LEF/LIB) for the Mixed Signal Module.

- This unique offering of Soft and Hard IP permits architectural design flexibility and seamless implementation in customer-specific design flow.

-

MIPI D-PHY℠ v2.5 IP Core

- This Tx/Rx transceiver complies with the MIPI Alliance C-PHY℠ v2.0 and D-PHY℠ v2.5 specifications, with world-class area and power dissipation, and is available for a range of foundry processes.

- This IP delivers 6 Gbps per lane for a max throughput of 24 Gbps in D-PHY℠ mode, and 6 Gsps per trio for a max throughput of 41.04 Gbps in C-PHY℠ mode.

-

MIPI C-PHY℠ v2.0 + D-PHY℠ v2.5 Combo IP Core

- This Tx/Rx transceiver complies with the MIPI Alliance C-PHY℠ v2.0 and D-PHY℠ v2.5 specifications, with world-class area and power dissipation, and is available for a range of foundry processes.

- This IP delivers 6 Gbps per lane for a max throughput of 24 Gbps in D-PHY℠ mode, and 6 Gsps per trio for a max throughput of 41.04 Gbps in C-PHY℠ mode.