MACsec IPSEC IP

Filter

Compare

31

IP

from

8

vendors

(1

-

10)

-

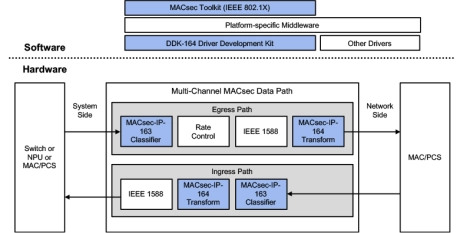

1.6T/3.2T Multi-Channel MACsec Engine with TDM Interface (MACsec-IP-364)

- The MACsec-IP-364 is a MACsec/IPsec engine developed specifically for high-speed, multi-rate and multi-port Ethernet devices.

- Its architecture provides an optimal multi-protocol solution for aggregate throughput for 1.6T and 3.2T.

- The MACsec-IP-364 is ideal for deployment in data center, enterprise and carrier network applications, as well as network-attached high-performance computing.

-

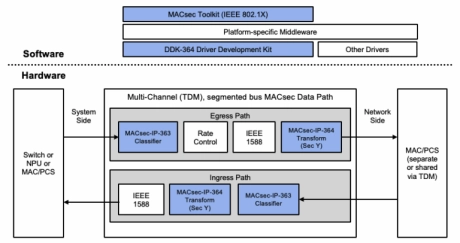

800G Multi-Channel MACsec Engine with TDM Interface

- Complete and fully compliant MACsec Packet Engine with classifier and transformation engines for rates of 100 to 800 Gbps, up to 64 channels, ready for FlexE

- All IEEE MACsec standards supported (including IEEE802.1AE-2018). Optional inclusion of Cisco extensions, IPsec ESP tunnel and transport mode with AES-GCM cipher

- Supplied with the Driver Development Kit to accelerate time to market. Rambus offers MACsec Toolkit for IEEE 802.1X key management

-

IEEE 802.1ae MACSEC IP Core for 40 Gbit Ethernet

- Complies with IEEE 802.1ae standard

- Based on the Algotronix AES-GCM-40G product

- Supports 256 bit keys as standard

- Targets high performance FPGA families from Xilinx and Altera.

-

IEEE 802.1ae MACSEC IP Core for 10 Gbit Ethernet

- Complies with IEEE 802.1ae standard

- Based on the Algotronix AES-GCM-1G product

- Supports 128 bit keys as standard, with 256 bit key option available

- Targets all modern FPGA families from Xilinx, Altera, Microsemi and Lattice

-

Multiple SecY IEEE 802.1ae MACSEC IP Core for 40Gbit Ethernet

- Complies with IEEE 802.1ae standard

- Based on the Algotronix AES-GCM-1G product

- Supports 128 bit keys as standard, with 256 bit key option available

- Targets all modern FPGA families from Xilinx, Altera, Microsemi and Lattice

-

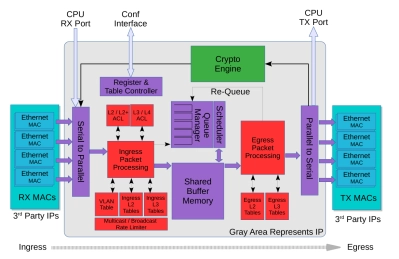

Ethernet Switch/Router IPSec/MACSec 9x10G + 2x40G

- 9 ports of 10 Gigabit Ethernet.

- 2 ports of 40 Gigabit Ethernet.

- Full wire-speed on all ports and all Ethernet frame sizes.

- Store and forward shared memory architecture.

- Support for jumbo packets up to 32733 bytes.

-

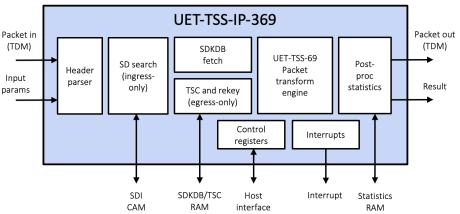

Multi-channel Ultra Ethernet TSS Complete Layer

- The UET-TSS-IP-369 (EIP-369) is an inline, high-performance, multi-channel packet engine that provides the complete TSS layer, bypass/drop and basic crypto processing at rates up to 1.6Tbps.

- The engine is designed for integration into the systems that require TSS processing for one or more ports. The engine is provided as separate ingress and egress data paths.

- The EIP-369 embeds the UET-TSS-IP-69 for the packet transformation.

-

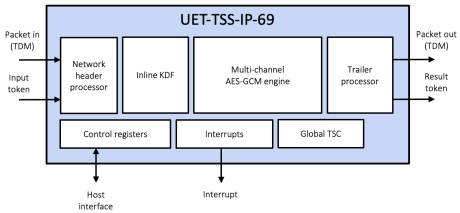

Multi-channel Ultra Ethernet TSS Transform Engine

- The UET-TSS-IP-69 (EIP-69) is a high-performance, multi-channel transform engine that provides the complete TSS packet transformation (including KDF and IP/UDP updates), bypass/drop and basic crypto processing at rates up to 1.6Tbps.

- The engine is designed for integration into the systems that require TSS processing for one or more ports. The engine is provided as separate ingress and egress data paths.

-

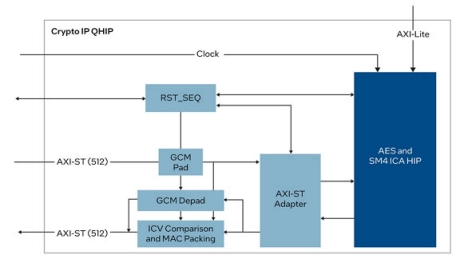

Symmetric Cryptographic Intel® FPGA IP

- The Symmetric Cryptographic Intel® FPGA IP is a hard IP core implementing AES and SM4 encryption and decryption

- Typically, the AES and SM4 standards are used to protect the confidentiality of network data in 5G, data center, and IoT applications, but can be used to secure any high-speed data in transit

- Additionally, the XTS profile can be used in data storage applications.

-

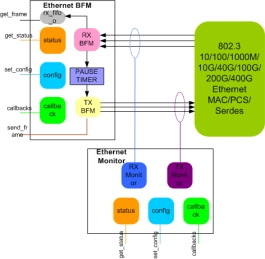

Ethernet - up to 800G Verification IP

- Supports 2.5G and 5G Speeds as per 802.3cb

- 2.5GBASE-KX

- 5GBASE-KR

- 2.5GBASE-T