LVDS IP

Filter

Compare

321

IP

from

64

vendors

(1

-

10)

-

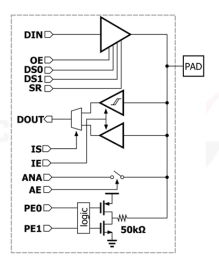

I/O Library with LVDS in SkyWater 90nm

- A SkyWater I/O Library combining standard GPIO, I2C-compatible ODIO, analog I/O, and integrated LVDS for robust mixed-signal and moderate-speed differ ential interfaces.

-

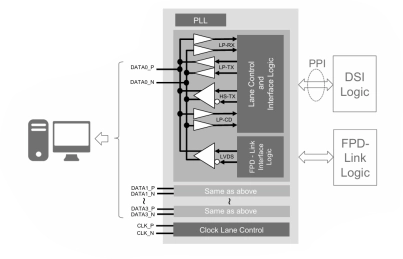

MIPI D-PHY and FPD-Link (LVDS) Combinational Transmitter for TSMC 22nm ULP

- Technology is TSMC 22nm ULP 1p10M.

- Supply voltage can be applied 1.0V for core voltage, 1.8V for IO voltage.

- Maximum data rate of each channel is 1.5Gbps at High-speed mode for MIPI D-PHY Transmitter.

- Data rate of each channel is 609Mbps for FPD-Link(LVDS).

-

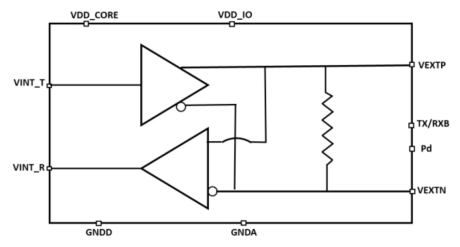

1 Gb/s LVDS Bidirectional IO on 12nm

- The ODT-LVDS-BID1G-12nm is a high-speed Bidirectional LVDS IO cell capable of operating up to 1 Gb/s.

- The ODT-LVDS-BID1G-12nm uses a high-speed signal path that can provide low jitter for input ranges of up to 1 Gb/s input.

- It also features small area and low power consumption.

- It includes the internal termination resistor and ESD protection diodes on the VEXTP and VEXTN pins.

-

TSMC N4P LVDS IO 1.5V MS add-on

- Synopsys Low Voltage Differential Signaling (LVDS) IO library is a high-frequency interface that uses differential signals for data transmission

- A few typical LVDS IO applications are in display monitors, printers, high-speed clock transfers, and high-speed SERDES

- Synopsys LVDS IO library is used to build an LVDS-based interface for high-speed interconnect applications

- This library is designed to optimize IO performance with a core voltage of 0.75 V and supports an IO supply voltage of 1.2V/1.5 V

-

TSMC N4P LVDS IO 1.5V

- Synopsys Low Voltage Differential Signaling (LVDS) IO library is a high-frequency interface that uses differential signals for data transmission

- A few typical LVDS IO applications are in display monitors, printers, high-speed clock transfers, and high-speed SERDES

- Synopsys LVDS IO library is used to build an LVDS-based interface for high-speed interconnect applications

- This library is designed to optimize IO performance with a core voltage of 0.75 V and supports an IO supply voltage of 1.2V/1.5 V

-

TSMC N4P LVDS IO 1.2V MS add-on

- Synopsys Low Voltage Differential Signaling (LVDS) IO library is a high-frequency interface that uses differential signals for data transmission

- A few typical LVDS IO applications are in display monitors, printers, high-speed clock transfers, and high-speed SERDES

- Synopsys LVDS IO library is used to build an LVDS-based interface for high-speed interconnect applications

- This library is designed to optimize IO performance with a core voltage of 0.75 V and supports an IO supply voltage of 1.2V/1.5 V

-

TSMC N4P LVDS IO 1.2V

- Synopsys Low Voltage Differential Signaling (LVDS) IO library is a high-frequency interface that uses differential signals for data transmission

- A few typical LVDS IO applications are in display monitors, printers, high-speed clock transfers, and high-speed SERDES

- Synopsys LVDS IO library is used to build an LVDS-based interface for high-speed interconnect applications

- This library is designed to optimize IO performance with a core voltage of 0.75 V and supports an IO supply voltage of 1.2V/1.5 V

-

TSMC N7 1.8V LVDS IO with CDM 7A, AG2 Platform

- Synopsys Low Voltage Differential Signaling (LVDS) IO library is a high-frequency interface that uses differential signals for data transmission

- A few typical LVDS IO applications are in display monitors, printers, high-speed clock transfers, and high-speed SERDES

- Synopsys LVDS IO library is used to build an LVDS-based interface for high-speed interconnect applications

- This library is designed to optimize IO performance with a core voltage of 0.75 V and supports an IO supply voltage of 1.2V/1.5 V

-

TSMC N6 1.8V LVDS IO with CDM 7A

- Synopsys Low Voltage Differential Signaling (LVDS) IO library is a high-frequency interface that uses differential signals for data transmission

- A few typical LVDS IO applications are in display monitors, printers, high-speed clock transfers, and high-speed SERDES

- Synopsys LVDS IO library is used to build an LVDS-based interface for high-speed interconnect applications

- This library is designed to optimize IO performance with a core voltage of 0.75 V and supports an IO supply voltage of 1.2V/1.5 V

-

TSMC N5A LVDS IO 1.2V/1.5V Metal Add-on

- Synopsys Low Voltage Differential Signaling (LVDS) IO library is a high-frequency interface that uses differential signals for data transmission

- A few typical LVDS IO applications are in display monitors, printers, high-speed clock transfers, and high-speed SERDES

- Synopsys LVDS IO library is used to build an LVDS-based interface for high-speed interconnect applications

- This library is designed to optimize IO performance with a core voltage of 0.75 V and supports an IO supply voltage of 1.2V/1.5 V