LPDDR3 Controller IP

Filter

Compare

101

IP

from

12

vendors

(1

-

10)

-

LPDDR3 Controller IIP

- Supports 100% of LPDDR3 protocol standard JESD209-3, JESD209-3B and JESD209-3C.

- Compliant with DFI version 3.1 or higher Specification.

- Supports all the LPDDR3 commands as per the specs.

- Supports up to 16 AXI ports with data width upto 512 bits.

-

LPDDR3 Controller

- x32 and x64 device targets

- 8Gb and 16Gb component support

- Source code delivery in Verilog

-

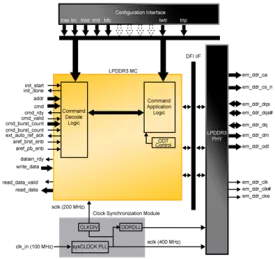

LPDDR3 SDRAM Controller

- Interfaces to Industry Standard LPDDR3 SDRAM components and modules compliant with the JESD-209.3 specification

- High-Performance LPDDR3 performance, up to 400 MHz/800 Mbps operation

- Supports automatic LPDDR3 SDRAM initialization and refresh

- Supports Deep Power Down Mode

-

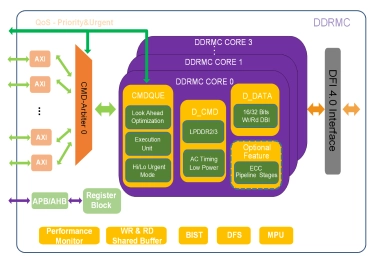

DDR Enhanced Protocol Controller (uPCTL2) supporting DDR4, DDR3, DDR2, LPDDR4, LPDDR3, and LPDDR2

- Select a complete multi-ported Enhanced Universal DDR Memory Controller offering 1 to 16 host ports, or join a third-party scheduler to a single-port Enhanced Universal Protocol Controller

- Support for JEDEC standard DDR2, DDR3, DDR4, LPDDR/Mobile DDR, LPDDR2, LPDDR3, and LPDDR4 SDRAMs

- Compatible with all Synopsys DDR PHYs (excluding DDR2/DDR PHYs) using DFI-compliant interfaces

-

Functional-Safety & Secure LPDDR3 Memory Subsystem

- Safe & Secure-LPDDR3 that is ready for ASIL (Automotive Safety Integrity Level) and secure by design

- Functional Safety out-of-the box design, with an extensive ASIL documentation package.

- Integrated security features into the controller. Characterized for extended operating conditions and long-term reliability.

-

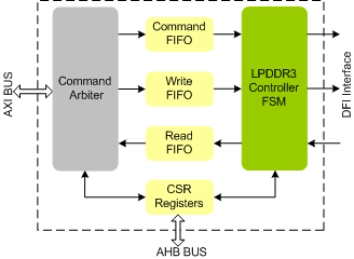

LPDDR3 IP solution

- Compatible with LPDDR3 up to 2133Mbps

- AXI compliant multi-ports, and data width, FIFO depth, command queue depth configurable

- DFI compliant interface between controller and PHY

- Support ECC (error correcting code)

-

LPDDR Controller

- Memory controller interface complies with DFI standard up to 5.0

- Application-optimized configurations for fast time to delivery and lower risk

- Sideband and in-line SEC/DED ECC

- Supports advanced RAS features including error scrubbing, parity, etc.

- Compliant to LPDDR5/4X/4/3 protocol memories

- Priority per command on Arm®AMBA® 4 AXI, AMBA 3 AXI

-

Performance Enhanced version of uMCTL2 supporting DDR4, DDR3, DDR2, LPDDR4, LPDDR3 and LPDDR2 for Automotive

- Select a complete multi-ported Enhanced Universal DDR Memory Controller offering 1 to 16 host ports, or join a third-party scheduler to a single-port Enhanced Universal Protocol Controller

- Support for JEDEC standard DDR2, DDR3, DDR4, LPDDR/Mobile DDR, LPDDR2, LPDDR3, and LPDDR4 SDRAMs

- Compatible with all Synopsys DDR PHYs (excluding DDR2/DDR PHYs) using DFI-compliant interfaces

-

Performance Enhanced version of DDR Enhanced Memory Ctl (uMCTL2) supporting DDR4, DDR3, DDR2, LPDDR4, LPDDR3, and LPDDR2

- Select a complete multi-ported Enhanced Universal DDR Memory Controller offering 1 to 16 host ports, or join a third-party scheduler to a single-port Enhanced Universal Protocol Controller

- Support for JEDEC standard DDR2, DDR3, DDR4, LPDDR/Mobile DDR, LPDDR2, LPDDR3, and LPDDR4 SDRAMs

- Compatible with all Synopsys DDR PHYs (excluding DDR2/DDR PHYs) using DFI-compliant interfaces

-

TSMC CLN40LPP 40nm LPDDR3 PHY - 2133Mbps

- Supports LPDDR3

- DFI 5.1 compliant

- Supports x4, x8 and x16 DRAMs

- Up to 72 bits wide and up to 4 ranks