LPDDR2 DRAM IP

Filter

Compare

6

IP

from

4

vendors

(1

-

6)

-

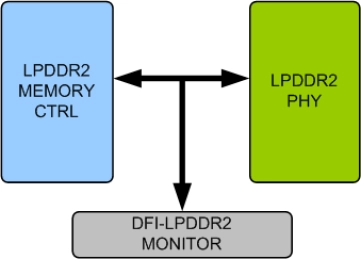

LPDDR2 DFI Verification IP

- Compliant with DFI version 2.1 or higher Specifications.

- Supports LPDDR2 devices compliant with JEDEC LPDDR2 SDRAM Standard JESD209-2F.pdf and JESD209-2E.pdf

- Supports for Read data-eye training

- Supports for Read gate training

-

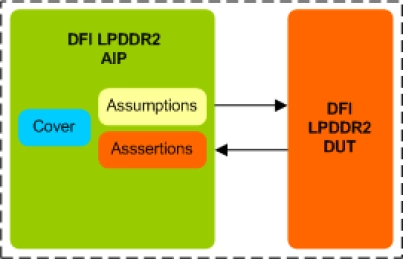

LPDDR2 DFI Assertion IP

- Specification Compliance

- Compliant with DFI version 2.1 or higher Specifications.

- Supports LPDDR2 devices compliant with JEDEC LPDDR2 SDRAM Standard JESD209-2F.pdf and JESD209-2E.pdf.

- Supports for Read data-eye training.

-

DDR and LPDDR 5/4/3/2 controllers for low power and high Reliability, Availability and Serviceability (RAS)

- Four memory controller offerings: uMCTL2: multi-ported memory controller supporting JEDEC standard DDR2, DDR3, DDR4, LPDDR, LPDDR2, LPDDR3, and LPDDR4, and LPDDR4X SDRAM and DIMM modules

- uPCTL2: Single-ported version of uMCTL2 with no internal scheduler; DDR5/4 controller: multi-ported memory controller supporting JEDEC standard DDR5, DDR4 SDRAMs and DIMM modules

- LPDDR5/4/4X controller: multi-ported memory controller supporting JEDEC standard LPDDR5, LPDDR4, and LPDDR4X SDRAMs

- High-bandwidth design with up to 64 CAM entries for Reads and 64 CAM entries for Writes, and latency as low as 6 clock cycles

-

DDR and LPDDR 5/4/3/2 controllers for low power and high Reliability, Availability and Serviceability (RAS) targeting automotive

- Four memory controller offerings: uMCTL2: multi-ported memory controller supporting JEDEC standard DDR2, DDR3, DDR4, LPDDR, LPDDR2, LPDDR3, and LPDDR4, and LPDDR4X SDRAM and DIMM modules

- uPCTL2: Single-ported version of uMCTL2 with no internal scheduler; DDR5/4 controller: multi-ported memory controller supporting JEDEC standard DDR5, DDR4 SDRAMs and DIMM modules

- LPDDR5/4/4X controller: multi-ported memory controller supporting JEDEC standard LPDDR5, LPDDR4, and LPDDR4X SDRAMs

- High-bandwidth design with up to 64 CAM entries for Reads and 64 CAM entries for Writes, and latency as low as 6 clock cycles

-

DDR4 PHY

- ? DDR4, LPDDR3, LPDDR2, DDR3, DDR3L, and DDR3U operation

- ?1.2V DDR4 SDRAMs operating at data rates up to 2400Mbps

- ?1.2V LPDDR2 SDRAMs operating at data rates up to 1066Mbps

- ?1.35V DDR3L SDRAMs operating at data rates up to 1866Mbps

-

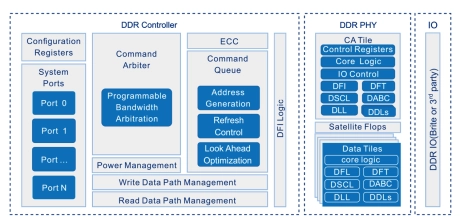

High Speed DDR Interface Solution

- Brite provides a complete DDR subsystem including not only controller, PHY and IO, but also corresponding tuning and configuration software. And this solution can support LPDDR2, DDR3, LPDDR3, DDR4 and LPDDR4/4x combo PHY with the data rate from 667Mbps to 4266Mbps.