LEON processor IP

Filter

Compare

11

IP

from

4

vendors

(1

-

10)

-

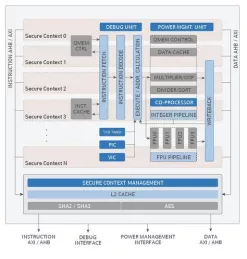

Secure Execution Processor

- The Geon™ Secure Execution Processor is a low-power, 32-bit processor IP core with built-in protection of sensitive code and data.

- It uses two or more cryptographically separated execution contexts for a high degree of security during code execution and for data storage and transfer to and from the processor.

-

Secure Execution Processor

- Two cryptographically isolated secure execution contexts

- Cryptographic primitives agnostic

- Lowest overhead implementation with single Keccak (SHA3) core

-

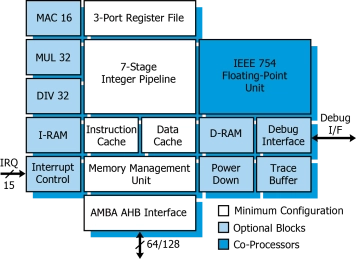

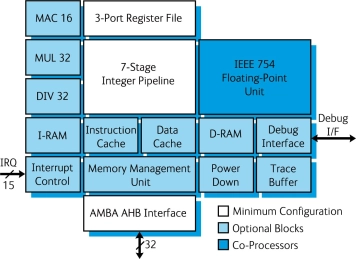

32-Bit SPARC V8 Processor

- SPARC V8 instruction set with V8e extensions and compare-and-swap

- Advanced 7-stage dual-issue pipeline

-

-

32-bit SPARC V8 processor

- The LEON3 processor offers robust fault tolerance and performance for space and high-reliability applications, including satellites and scientific instruments.

- The LEON3 is a synthesisable VHDL model of a 32-bit processor compliant with the SPARC V8 architecture. The model is highly configurable and particularly suitable for system-on-a-chip (SOC) designs.

-

Highest performance real-time processor

- The highest performance real-time processor – double the total performance of Cortex-R7.

-

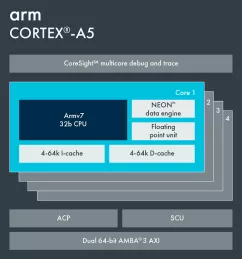

Smallest, Lowest Power ARM Multicore Applications Processor

- Feature set of Cortex-A9 for half the size and power - Fully feature compatible with Cortex-A9 processor, provides 70-80% of Cortex-A9 performance and significantly higher efficiency.

- Most scalable and configurable Armv7-A processor - The Cortex-A5 processor is extremely configurable and scalable to meet performance, power and area requirements for cost sensitive, low power applications.

- Available in single core and multi core configurations - The Cortex-A5 processor is available in two variants: as a single core Cortex-A5 UP processor and as Cortex-A5 MP where it can scale up to four processor cores in a cluster.

-

Configurable AMBA bus SoC platform

- Robust and fully synchronous single-edge clock designs

- Up to 125 MHz in FPGA and 400 MHz on 0.13 um ASIC technologies

- Fault-tolerant and SEU-proof version

- Symmetric Multi-processor support (SMP)

-

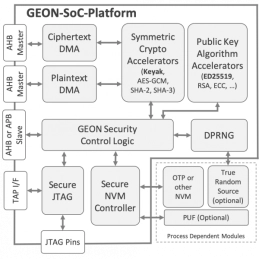

SoC Security Platform / Hardware Root of Trust

- GEON-SoC is an area-efficient, processor-agnostic, hardware root of trust for SoC designs.

- It implements secure boot and can optionally be enhanced to support firmware decryption and secure debug, or to act as a post-boot hardware security module (HSM).

-

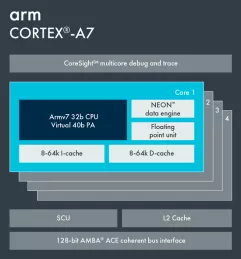

Arm Cortex-A7

- In-order 8 stage pipeline - Improved dual issue, branch prediction and memory system performance. It features 64-bit load-store path, 128-bit AMBA 4 AXI buses and increased TLB size (256 entry).

- Integrated, Configurable Size Level 2 Cache Controller - Provides low-latency and high-bandwidth access to up to 1MB of cached memory in high-frequency designs, or designs needing to reduce the power consumption associated with off-chip memory access. The L2 cache is optional on Cortex-A7.

- Support Armv7-A extensions - Hardware Virtualization and Large Physical Address Extensions (LPAE) enables the processor to access up to 1TB of memory.

- big.LITTLE technology - First LITTLE processor architecturally compatible with compatible with Cortex-A15 and Cortex-A17 for various big.LITTLE processor combinations.