LDPC IP

Filter

Compare

134

IP

from

25

vendors

(1

-

10)

-

5G LDPC Decoder

- Low power design for HW implementation

- Minimum HW cost in ASIC implementation for LDPC decoder

- Optimized TDEC early termination algorithms to minimize power consumption

- Flexible HW architecture

-

NavIC LDPC Decoder

- Throughput matching the required specifications.

- Bit-Error-Rate (BER) and Block-Error-Rate (BLER) performance meet the required specifications.

- Compliant with 'ISRO-NAVIC-ICD-SPS-L1-1.0' standard

-

Flash Memory LDPC Decoder IP Core

- Quasi cyclic (QC) – Algebraic constructed – LDPC Code

- Regular Parity Check Matrix

- Codeword length: 16 K

- Code rate 0.953

- No or very low error floor

- Parallel/Layered decoding

-

LDPC Intel® FPGA IP

- Low-density parity-check (LDPC) codes are linear error correction codes that allow you to transmit messages over noisy channels.

- Intel's 5G Low-Density Parity Check (LDPC) Intel FPGA Intellectual Property (IP) core is a high-throughput encoder or decoder that is compliant with 3rd Generation Partnership Project (3GPP) 5G specification.

-

5G LDPC Intel® FPGA IP

- Low-density parity-check (LDPC) codes are linear error correcting codes that help you to transmit and receive messages over noisy channels

- The 5G LDPC and LDPC-V Intel® FPGA IP implement LDPC codes compliant with the 3rd Generation Partnership Project (3GPP) 5G specification for integration in your wireless design.

- LDPC codes offer better spectral efficiency than Turbo codes and support the high throughput for 5G new radio (NR).

-

DVB-S2X Wideband LDPC/ BCH Encoder

- Compliant with ETSI EN 302 307’

- Compliant with ETSI EN 302 307-2’

- Supports BCH-LDPC all code rates for digital video broadcasting

-

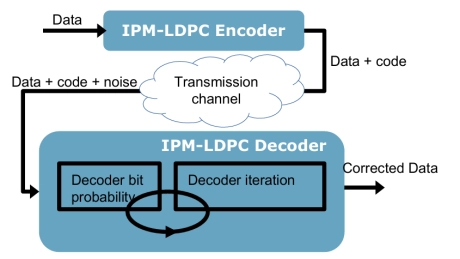

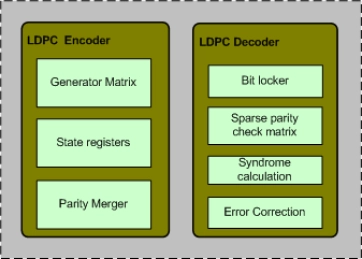

LDPC Encoder/Decoder IP Core

- IPM-LDPC for NandFlash Storage: Adaptable BER, Up to 6 checks per bit, customizable data path

- IPM-LDPC for short code: option to be full asynchronous, option to be in 3 clock cycles

- fully configurable: matrix generator, data path, number of iteration checks, packet size

-

LDPC (1723,2048) IIP

- Compliant with IEEE Standard 802.3.2018 Ethernet specification.

- Supports full LDPC functionality.

- Supports the Lower density parity check (1723,2048).

- Supports the parity generation of 325 bits.

-

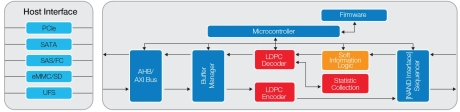

eMMC LDPC Encoder/Decoder

- Supports data rates from 50 MB/s to 9.0 GB/s.

- Enables custom LDPC core development for specific requirements.

- Wide range of codeword sizes.

- Maximum supported parity.

-

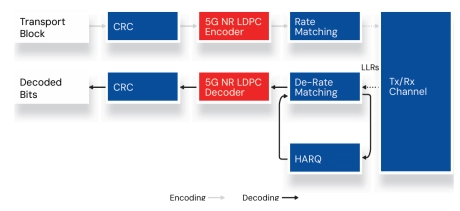

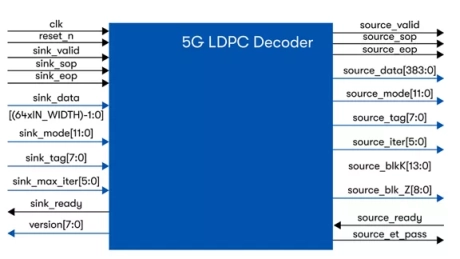

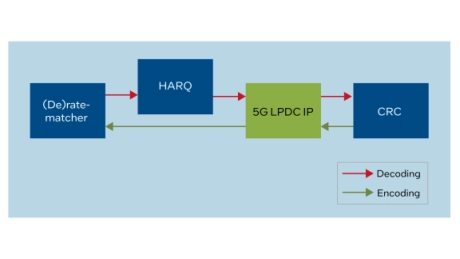

LDPC Decoder for 5G NR and Wireless

- The 5G NR LDPC Decoder IP Core offers a robust solution for LDPC decoding, featuring a dedicated LDPC decoder block for optimal performance.

- It employs the Min-Sum LDPC decoding algorithm to ensure efficient decoding.

- The core allows for programmable internal bit widths at compile time, though the default values are usually sufficient.