Intrinsic ID IP

Filter

Compare

1

IP

from

1

vendors

(1

-

1)

-

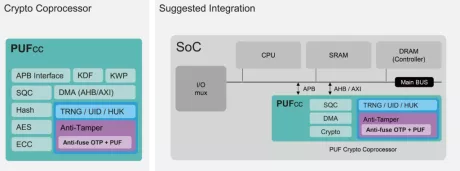

TLS 1.3 Compliant Crypto Coprocessor

- NIST CAVP certified and OSCCA standard compliant crypto engine suite

- Includes private/public key ciphers, message authentication code, hashes, and key derivation

- Key wrapping function for the secure export of keys

- Public-key coprocessor for digital signatures and key agreements over elliptic/Edward curves