Interconnect IP

Filter

Compare

785

IP

from

88

vendors

(1

-

10)

-

Universal Chiplet Interconnect Express PHY IP - GLOBALFOUNDRIES® 22FDX®

- Delivered as Hardmacro IP

- Implementation of the physical layer of the UCIe standard from Raw D2D Interface (RDI) to electrical interface of UCIe main band (MB) and sideband (SB)

- Includes TX and RX side

-

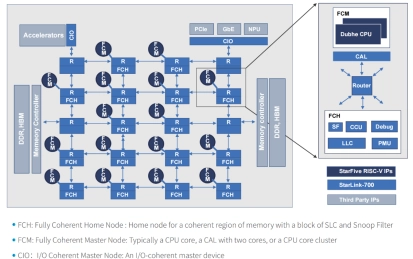

High-scalable, high-performance Interconnect fabric IP with cache coherence support

- High bandwidth, low power consumption, low latency

- Support Component Aggregation Layer (CAL)

- Topology: Mesh

- Support multiple I/O Coherent Master Nodes (CIO)

- Maximum node count: 12x12

-

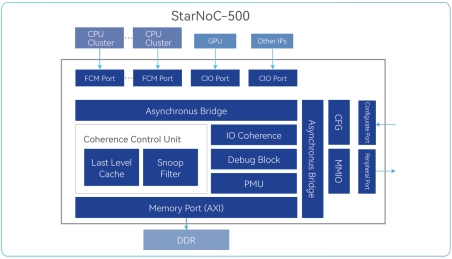

Interconnect fabric IP with cache coherence support

- StarNoC-500 is the vendor's first self-developed interconnect fabric IP with cache coherence support, supporting the construction of multi-cores and SoC.

-

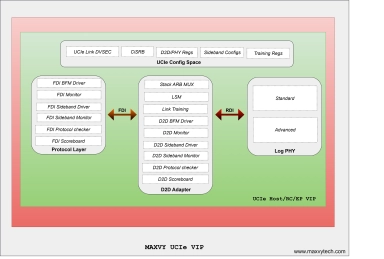

Universal Chiplet Interconnect Express(UCIe) VIP

- The UCIe VIP , a state-of-the-art solution that offers a comprehensive set of features and capabilities to ensure the quality and performance of your UCIe designs

- The UCIe VIP is fully compliant with UCIe Specification version 1.0 and supports all the layers of the UCIe stack, such as FDI, RDI, LogPHY, PCIe, and CXL protocols

- The UCIe VIP is also very user-friendly and flexible, with simple APIs, easy integrations, and configurable parameters

-

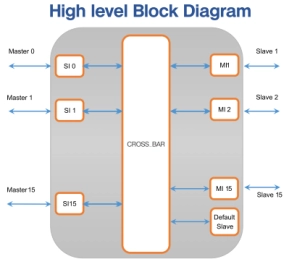

AXI Interconnect

- The AXI MATRIX-IP component is a multi-layer interconnect implementation of the AXI protocol, which is designed for high-performance, high-frequency system designs.

- AXI MATRIX-IP is highly configurable with the capacity to handle up to 16 Masters and Slaves. IP can be configured to support AXI3, AXI4-Lite or AXI4

-

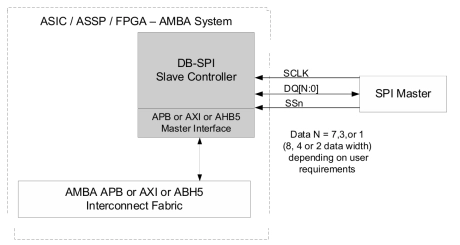

SPI Slave IP transfers to/from a AMBA APB, AXI, or AHB Interconnect

- The DB-SPI-S-AMBA-BRIDGE is a Serial Peripheral Interface (SPI) Controller Verilog IP Core supporting only Slave SPI Bus transfers (both Full Duplex and Half Duplex) to/from a AMBA APB, AXI, or AHB Interconnect.

- The DB-SPI-S-AMBA-BRIDGE contains dual clock Transmit/Receive FIFOs and Finite State Machine control to process incoming SPI transmit/receive transactions, and a AMBA Master Interface (i.e. APB, AXI, AHB5) to read or write the SPI payload data with respect to the AMBA Interconnect. No processor is required for configuration or control; the DB-SPI-S-AMBA-BRIDGE operates autonomously from reset.

-

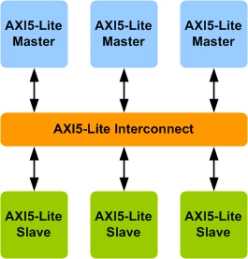

AMBA AXI5-Lite Interconnect Verification IP

- Compliant with the latest ARM AXI5-Lite Protocol Specification.

- Supports AXI5-Lite Master, Slave, Interconnect, Monitor and Checker.

- Supports all AXI5-Lite data and address widths.

- Supports all protocol transfer types, burst types, burst lengths, burst sizes and response types.

-

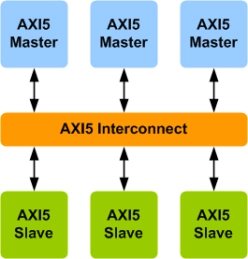

AMBA AXI5 Interconnect Verification IP

- Compliant with the latest ARM AMBA AXI5 Protocol Specification.

- Supports AXI5 Master, Slave, Interconnect, Monitor and Checker.

- Supports all ARM AMBA AXI5 data and address widths.

- Supports all protocol transfer types, burst types, burst lengths, burst sizes and response types.

-

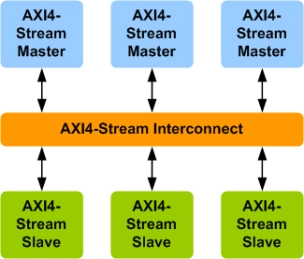

AMBA AXI4-Stream Interconnect Verification IP

- Compliant with the latest ARM AMBA AXI4-Stream Protocol Specification.

- Supports AXI4-Stream Master, Slave, Interconnect, Monitor and Checker.

- Supports all ARM AMBA AXI4-Stream data widths.

- Support for all Data streams including Byte stream, Continuous aligned stream, Continuous unaligned stream and Sparse stream.

-

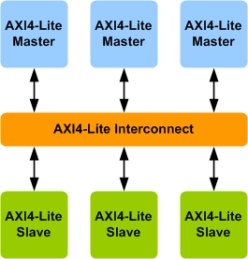

AMBA AXI4-Lite Interconnect Verification IP

- Compliant with the latest ARM AMBA AXI4-Lite Protocol Specification.

- Supports AXI4-Lite Master, Slave, Interconnect, Monitor and Checker.

- Supports all ARM AMBA AXI4-Lite data and address widths.

- Supports all protocol transfer types and response types.