IEEE 802.3 Ethernet IP

Filter

Compare

233

IP

from

30

vendors

(1

-

10)

-

100G Reed-Solomon Codec for Ethernet IEEE 802.3 Clause 91 (803.3bj)

- FEC Sublayer for 100GBASE-CR4 and 100GBASE-KR4 PHY (clause 91 of the IEEE 802.3bj standard).

- 100G Ethernet MAC-friendly interface

-

IEEE 802.3 Clause 74 FEC

- The IP core supports encoding and decoding of the (2112,2080) Fire code defined in IEEE 802.3 Clause 74

- Suitable for 10GBASE-R, 25GBASE-R, 40GBASE-R, 50GBASE-R and 100GBASE-R Ethernet PHYs and 16G Fibre Channel PHYs

- Burst errors of up to 11 bits can be corrected

- All alignment, transcoding, and scrambling functions are performed within the core

-

50G IEEE 802.3 Reed-Solomon Forward Error Correction

- Low latency

- Accessible as an integrated feature in the 50G Ethernet Subsystem

- Configuration and status bus

- Selectable AXI4-Lite interface for status output

-

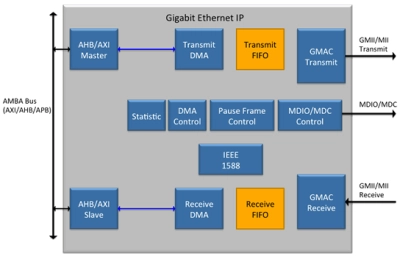

Gigabit Ethernet with IEEE 1588 and AVB

- The Gigabit Ethernet Media Access Controller IP is compliant with the Ethernet IEEE 802.3-2008 standard and supports protocol extensions for Audio Video Bridging (AVB).

- The Gigabit Ethernet IP provides a 10/100 Mbps Media Independent Interface (MII) and a 1000 Mbps Gigabit Media Independent Interface (GMII).

-

Gigabit Ethernet 802.3 MAC Controller IP

- Supports CPU local bus interface for controlling Ethernet MAC internal registers.

- Supports 32-bit memory local bus interface

- Comply with IEEE 802.3u MII interface.

- Support Reduced MII interface

-

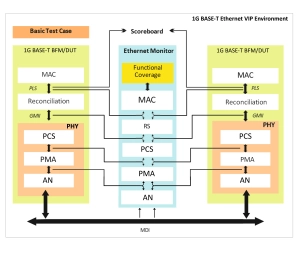

1G BASE-T Ethernet Verification IP

- The 1G BASE-T Ethernet Verification IP provides deliverables an effective & efficient way to verify the components interfacing with the Ethernet interface of an IP or SoC.

- The 1G Ethernet VIP is fully compliant with the IEEE standard 802.3 specification.

- This VIP is lightweight with easy plug -and- play interface so that there is no hit on the design cycle time.

-

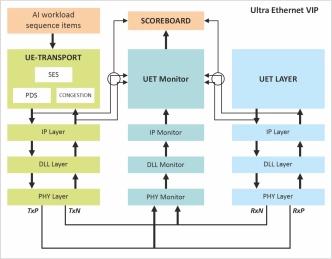

Ultra Ethernet Verification IP

- The Ultra Ethernet (UE) Verification IP provides an effective & efficient way to verify the components interfacing with Ethernet interface of an IP or SoC.

- The UE VIP is compliant with IEEE standard 802.3-2018 & UE Specifications V1.0.

- This VIP is light weight with easy plug-and-play interface so that there is no hit on the design cycle time.

-

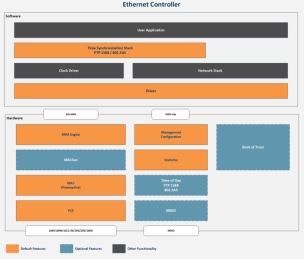

Ethernet Controller

- The Ethernet Controller is an ASIC proven high-performance, feature-rich network interface solution designed to deliver reliable, low-latency Ethernet connectivity across a broad range of embedded and enterprise applications.

- Comcores offers controllers ranging from 10M to 800G enabling seamless integration into systems requiring Ethernet connectivity.

-

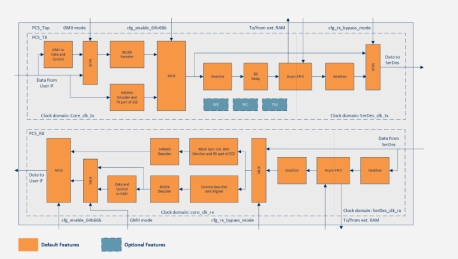

Ethernet PCS 1G/2.5G/5G/10G/25G & CPRI 7.0

- A combined silicon agnostic implementation of the PCS layer compliant with Ethernet standard IEEE 802.3-2018 and CPRI Specification V7.0 based solution

- The IP-core supports 1G, 2.5G, 5G, 10G, and 25G Ethernet data rates as well as CPRI data rate option 1 (614.14M) to option 10 (24.33024G).

-

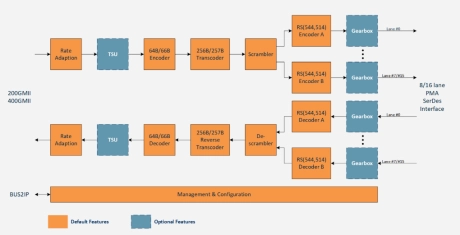

Ethernet PCS 200G/400G

- The 200G/400G Ethernet PCS IP core is a silicon agnostic implementation of the Physical Coding Sublayer (PCS) described in the Ethernet standard IEEE 802.3-2020 and its compliant with Clause 117 and Clause 119 of IEEE 802.3 specification.

- Ethernet PCS 200G/400G IP provides an interface between the Media Access Control (MAC) and Physical Medium Attachment (PMA) through a 8 or 16-lane parallel interface and offers a 200GMII or 400GMII interface on the other side.