IEEE 1149.7 IP

Filter

Compare

7

IP

from

4

vendors

(1

-

7)

-

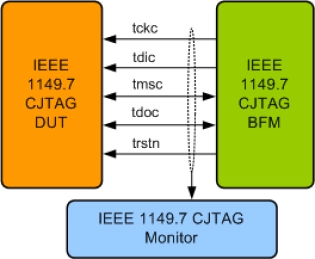

CJTAG (IEEE 1149.7) Verification IP

- Fully compatible with IEEE 1149.7 standard.

- Can be used as TAP controller (slave) or TAP instruction/data generator (Master) for CJTAG.

- Comes with CJTAG monitor to check and report any protocol violation.

- Supports TAP.7 capability classes T0 to T5

-

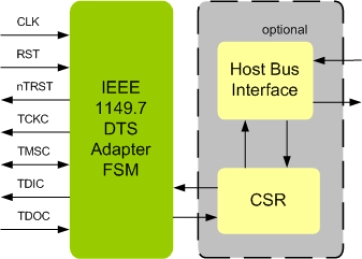

IEEE 1149.7 DTS ADAPTER IIP

- Compliant with IEEE 1149.7 standard specification.

- Full IEEE 1149.7 DTS Adapter functionality.

- Supports IEEE 1149.7 classes T0 to T5.

- Supports Reset and Escape sequences generation of TAP controller.

-

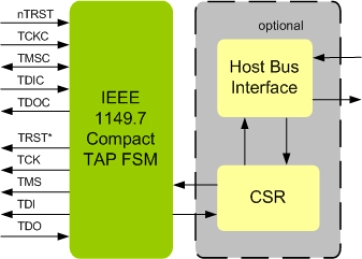

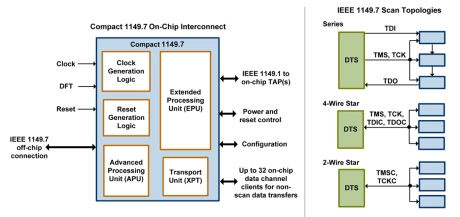

IEEE 1149.7 COMPACT TAP IIP

- Compliant with IEEE 1149.7 standard specification.

- Supports TAP.7 capability classes T0 to T5.

- Supports Reset and Selection Unit (RSU) for class T0 optional features.

- Supports Extended Protocol Unit (EPU) for classes T0 to T3.

-

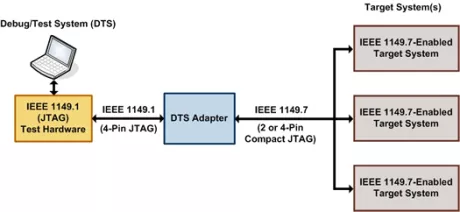

cjTAG IEEE 1149.7 DTS Adapter

- IEEE 1149.1 interface to existing test/debug hardware

- IEEE 1149.7 interface to target system(s)

- Supports all IEEE 1149.7 scan formats

- Supports all IEEE 1149.7 scan topologies

-

cjTAG IEEE 1149.7 Compact TAP Controller

- Supports IEEE 1149.7 classes 0–5 (selected through hardware configuration parameter)

- Partitioned along IEEE 1149.7-specified functional boundaries (so that only the required hardware is included):

- Supports all mandatory and optional scan formats: JScan0–3, SScan0–3, OScan0–7, and MScan

- Supports all mandatory and optional cJTAG commands

-

eFlash BIST IP

- The BIST can realize all eFlash testing items, covering UMC’s 40nm and 55nm processes, as well as SST’s 0.11um and 0.18um processes, and customized embedded eFlash IP wafer software testing and final testing.

- The BIST features a flexible serial interface, reducing the need for IC test pins and increasing testing flexibility.

-

JTAG 2-Wire to 4-Wire Adapter

- IEEE 1149.1 and IEEE 1147.7 compatible.

- Small logic overhead.

- Clock frequencies to 25MHz.