HD video decoder IP

Filter

Compare

42

IP

from

16

vendors

(1

-

10)

-

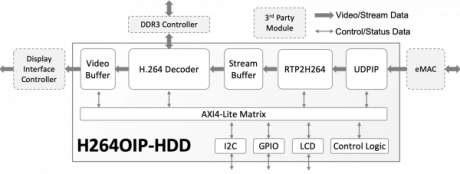

H.264 Video Over IP – HD Decoder Subsystem

- This Video Over IP Subsystem integrates H.264 Decompression, Transport Stream and RTP/UDP/IP de-capsulation to enable the rapid development of complete video streaming products.

- Hardware reference designs and customization services complete the solution.

-

Video Decoder IP optimized for HD use cases

- D100 Series is the ultimate multi-format, multi-stream real-time hardware decoder IP core, for all semiconductor manufacturers looking to integrate a high-performance video decoding solutions into their chips.

- Built upon a true multi- format architecture, the D100 Series Decoder IP core provides highly flexible solution up to HD/5Mpixels resolution and selectable video codecs.

- D100 Series supports H.264, HEVC, VP9, AV1 and JPEG formats.

-

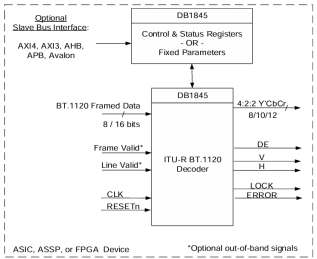

ITU-R BT.1120 Decoder – HD 1920x1080p

- The DB1845 ITU-R BT.1120 / BT.656 Decoder IP Core decodes ITU-R BT.1120 and BT.656 digital video uncompressed NTSC and PAL video, extracting Y’CbCr 4:2:2 video components and frame timing & status signals.

-

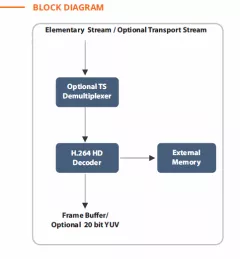

H.264 HD DECODER - Supports 1080p60. 4:2:2. 10 Bits

- Standard: H.264/MPEG-4 Part 10 (ISO/IEC 14496-10 & ITU-T H.264)

- Profiles: Constrained Baseline, Main & High profiles

- Video Resolutions: Up to 1920 x 1080

- Frame Rate: Up to 60 fps

-

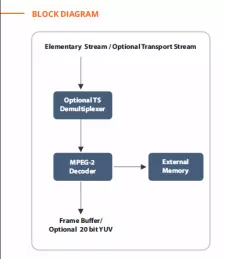

MPEG-2 HD Decoder - Supports 1080p60. 4:2:2. 8-bit,

- Standard: ISO/IEC 13818-2 (H.262)

- Profiles: Simple, Main and 4:2:2

- Video Resolutions: Up to 1920 x 1080

- Frame Rate: Up to 60 fps

-

JPEG 2000 HD decoder board

- • PCIe board, 4 lanes

- • Input: j2c codestream (adapted Digital Cinema Profile)

- • Output: uncompressed images or video in YCbCr 4:2:2 format

- • Custom image size up to 1080p in a single tile

-

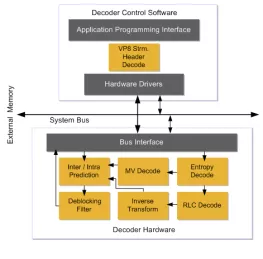

WebM VP8 Video Decoder Hardware IP

- Silicon area: 383kGates, 40kBytes of single port SRAM

- Synthesizable clock frequency: up to 290 MHz (TSMC65nm LP, topographical synthesis)

- Easy back-end: Single clock domain;low number of isolated single port SRAM and clock gating elements; no dual port memories.

- Performance configuration: choose internal memory size according to your resolution requirement - up to 2160p.

-

TicoXS | JPEG XS HD Encoder / Decoder IP-cores

- Near-Lossless up to 6:1.

- Visually lossless up to 12:1

- Color format : RGB,YUV, YCbCr, 444 / 422 /420 / monochrome

- Smooth lossy compression beyond

-

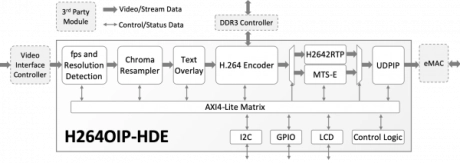

H.264 Video Over IP – HD Encoder Subsystem

- This Video Over IP Subsystem integrates H.264 compression, Transport Stream and RTP/UDP/IP encapsulation to enable the rapid development of complete video streaming products.

- Hardware reference designs and customization services complete the solution.

-

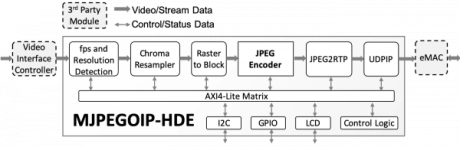

Motion JPEG Over IP – HD Video Encoder Subsystem

- This Video Over IP Subsystem employs JPEG compression and RTP/UDP/IP encapsulation to enable the rapid development of complete motion JPEG video streaming products. Hardware reference designs and customization services complete the solution.

- The subsystem uses CAST’s JPEG-E-S, JPEG2RTP, and UDPIP IP cores.