Motion JPEG Over IP – HD Video Encoder Subsystem

This Video Over IP Subsystem employs JPEG compression and RTP/UDP/IP encapsulation to enable the rapid development of motion JPEG…

Overview

This Video Over IP Subsystem employs JPEG compression and RTP/UDP/IP encapsulation to enable the rapid development of complete motion JPEG video streaming products. Hardware reference designs and customization services complete the solution.

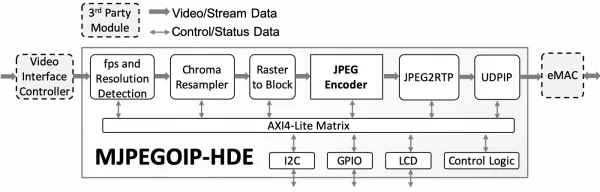

The subsystem uses CAST’s JPEG-E-S, JPEG2RTP, and UDPIP IP cores. Flexible interfaces allow easy integration of video and network controllers; the cores’ AMBA® AXI4-Lite™ slave interfaces allow a host processor to access all control and status registers. An optional custom logic module allows standalone, processor-free operation and provides access to control and status registers via UDP packets. Video and stream data are transferred among the subsystem’s modules using AXI-Stream, making removing or adding modules straightforward.

The produced stream can be decoded using Motion JPEG-compatible software viewers (e.g. VLC).

Key features

- Complete subsystem streams 1080p video with lower latency, less power consumption, and fewer silicon resources than hardware video codecs or software compression.

- Motion-JPEG Video Compression

- Ultra-low, sub-frame latency capable

- No frame buffering, eliminates the need for external DRAM

- Quality equivalent to video compression for compression ratios up to 20:1

- RTP encapsulation according to RFC 2435

- Compressed stream decodable by compliant software decoders/viewers such as VLC

- Host interface via AXi4-Lite or processor-free UDP-controlled operation

- AXI4-ST bus for Video & Stream

- Customization Options

- Integration with Video-In Controllers (e.g., DVI, HDMI, MIPI-CSI, or SDI)

- Integration with IP-based MAC controllers (e.g., Ethernet or 802.11 WiFi)

- Multiple video channels, different video preprocessing modules, or different compression algorithms

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Video Processing IP core

Configurable Processors for Video Processing SOCs

FPGA-based video surveillance comes of age

Picking the right MPSoC-based video architecture: Part 1

Video encoding with low-cost FPGAs for multi-channel H.264 surveillance

Analysis: ARC's Configurable Video Subsystems

Frequently asked questions about Video Processing IP

What is Motion JPEG Over IP – HD Video Encoder Subsystem?

Motion JPEG Over IP – HD Video Encoder Subsystem is a Video Processing IP core from CAST listed on Semi IP Hub.

How should engineers evaluate this Video Processing?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Video Processing IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.