Ethernet MAC IP

Filter

Compare

625

IP

from

73

vendors

(1

-

10)

-

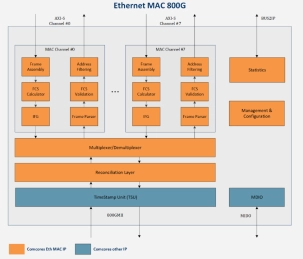

Ethernet MAC 800G

- The 800G Ethernet Media Access Control (MAC) IP core provides a comprehensive and flexible solution for implementing the IEEE 802.3 MAC layer for high-speed Ethernet required in demanding applications such as hyperscale data centers, high-performance computing (HPC), and Artificial Intelligence (AI) / Machine Learning (ML) clusters.

-

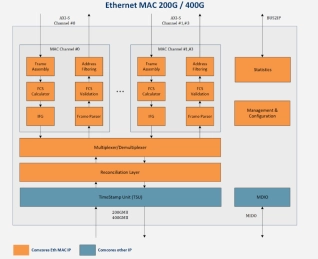

Ethernet MAC 200G/400G

- The 200G/400G Ethernet Media Access Control (MAC) IP core provides a comprehensive and flexible solution for implementing the IEEE 802.3 MAC layer for high-speed Ethernet required in demanding applications such as hyperscale data centers, high-performance computing (HPC), and Artificial Intelligence (AI) / Machine Learning (ML) clusters.

-

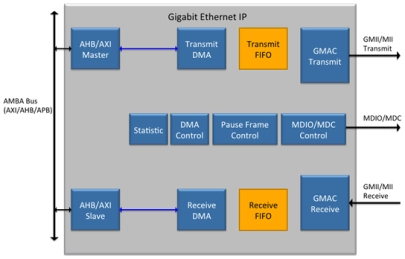

Gigabit Ethernet MAC IP Core

- The silicon-proven Gigabit Ethernet IP core provides a 10/100 Mbps Media Independent Interface (MII) and a 1000 Mbps Gigabit Media Independent Interface (GMII).

- It also supports optional Reduced MII (RGMII), and Serial GMII (SGMII).

-

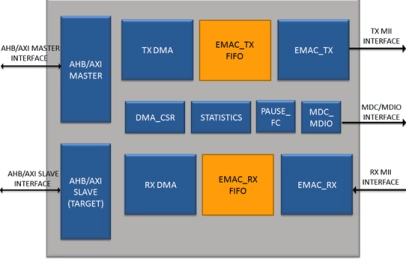

10/100 Ethernet MAC IP core

- The 10/100 Ethernet Media Access Controller (MAC) IP core is compliant with the Ethernet IEEE 802.3-2002 standard and has passed interoperability testing at UNH-IOL.

- The 10/100 Ethernet IP core provides an 10/100 Mbps Media Independent Interface (MII) and an optional processor interface; it also supports Reduced MII (RMII) and Serial MII (SMII).

-

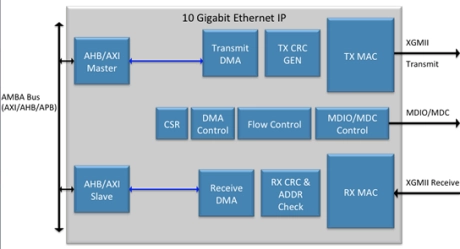

10 Gigabit Ethernet MAC IP Core

- The 10 Gigabit Ethernet (XGMAC) IP core is compliant with the Ethernet IEEE 802.3-2008 standard and provides an interface between AHB/AXI Bus and the 10 Gigabit Media Independent Interface (XGMII) using a powerful 64-bit Scatter Gather DMA.

- The 10 Gigabit Ethernet IP core is designed for applications such as integrated networking devices, host bus adapters, PCI-Express Ethernet controllers, and Ethernet adapter cards.

-

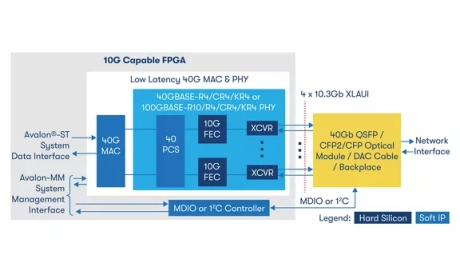

40G Ethernet MAC and PHY FPGA IP Core

- The 40G Ethernet MAC and PHY FPGA IP core offers IEEE 802.3ba-2010

- 40 Gbps Ethernet is an industry standard and is compliant for media access control (MAC) and PHY (PCS+PMA) functions

- It enables an FPGA to interface to another device over a copper or optical transceiver module

- The IP supports IEEE 1588 v2 standard with two-step timestamping as well as backplane capability on a variety of Stratix® or Arria® FPGAs.

-

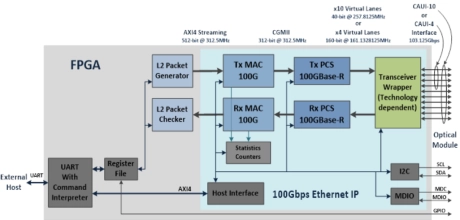

100 G Ethernet MAC & PCS IP Core

- The 100 Gbps Ethernet IP solution offers a fully integrated IEEE802.3ba compliant package for NIC (Network Interface Card) and Ethernet switching applications.

- Ethernet IP solution implements two user (application) side interfaces. The register configuration and control port is a 32-bit AXI4-Lite interface.

-

10 Gigabit Ethernet MAC ASIL B Compliant Controller for Automotive Applications

- Compliant with the IEEE 802.3az-2010 specification

- Supports 1/2.5/5/10G data rates

- Supports VLAN tag processing Checksum insertion and AVB

- Supports IEEE 1588 PTP

-

10 Gigabit Ethernet MAC

- Compliant with the IEEE 802.3az-2010 specification

- Supports 1/2.5/5/10G data rates

- Supports VLAN tag processing Checksum insertion and AVB

- Supports IEEE 1588 PTP

-

Ethernet MAC 10/100/1G Quality-of-Service

- Compliant with IEEE specifications

- Compliant with Arm AMBA specifications

- RGMII/RTBI specification version 2.6 from HP/Marvell

- RMII specification version 1.2 from RMII consortium