Dolby Atmos for PCs IP

Filter

Compare

42

IP

from

5

vendors

(1

-

10)

-

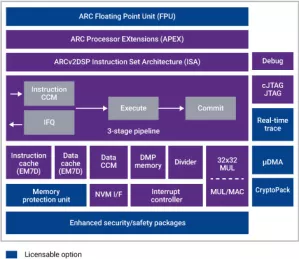

ARC EM7D DSP Enhanced 32-bit processor core with caches, ARCv2DSP ISA, for low power embedded DSP ap

- Dual 32x16 XMAC component supports up to two 32x16 MAC operations per instructions and supports all the 32x16 & dual 16x16 MAC instructions

- Dual XMAC built in shifters and 80-bit accumulators allow pseudo floating-point operations to be performed which greatly expanded dynamic range

- RAM configuration optimized for efficient area and power

- Improved system efficiency with enhanced ARM® AMBA® AXI™/AHB™ bus bridges

-

ARC EM5D Enhanced 32-bit processor core, ARCv2DSP ISA, for low power embedded DSP applications

- Dual 32x16 XMAC component supports up to two 32x16 MAC operations per instructions and supports all the 32x16 & dual 16x16 MAC instructions

- Dual XMAC built in shifters and 80-bit accumulators allow pseudo floating-point operations to be performed which greatly expanded dynamic range

- RAM configuration optimized for efficient area and power

- Improved system efficiency with enhanced ARM® AMBA® AXI™/AHB™ bus bridges

-

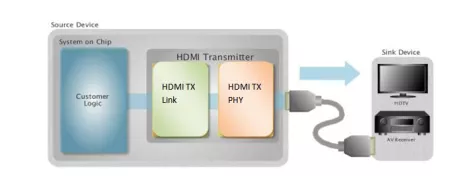

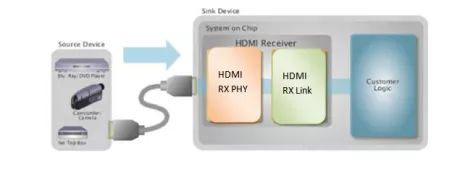

HDMI 1.4 transmitter IP core is ideal for DVD, Blu-Ray Disc players, set-top boxes, A/V receivers

- Video Interface

- Digital Audio Interface

- Other key features

-

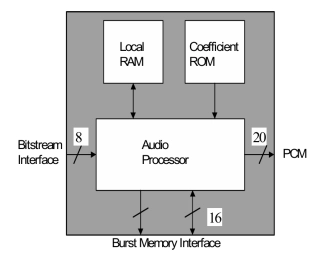

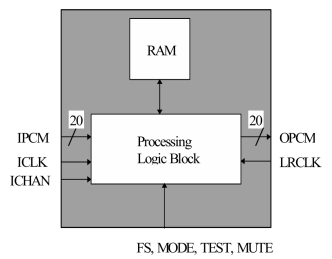

Dolby Digital/AC-3/MPEG Audio Decoding Core

- The J1 is a core cell design of an application specific signal processor which performs both Dolby Digital/AC-3 and MPEG audio decompression in a single design.

- The J1 is capable of decoding all AC-3 bitstreams with full support for bitstreams encoded with 5.1 channels and data rates of up to 640kb/s.

- The J1 downmixing capability produces stereo output in either normal or Pro-Logic compatible modes, making it ideal for DVD and set-top applications.

-

3-D Audio Processing Core

- The J5 is a core cell design of an application specific signal processor which performs both Trusurround(TM) and SRS® 3-D audio virtualization processing in a single design.

- The 3-D processing allows users to enjoy benefits of a multi-channel sound source with only two reporduction channels.

-

HDMI ver1.3 Transmitter IP

- HDMI version 1.3a, HDCP revision 1.2 and DVI version 1.0 compliant transmitter

- Supports DTV from 480i to 1080i/p HD resolution, and PC from VGA to UXGA

- Programmable 2-way color space converter

- Compliant with EIA/CEA-861D

-

-

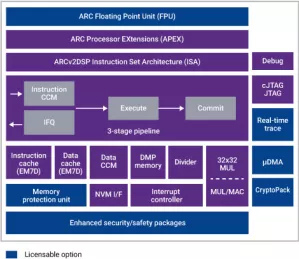

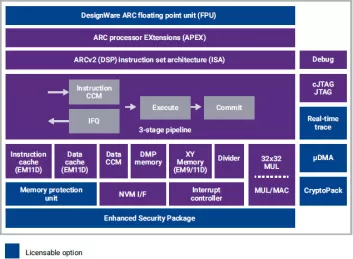

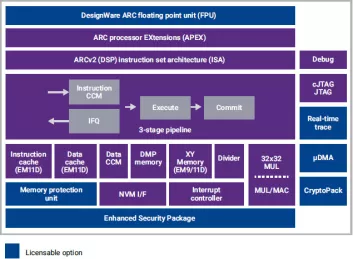

ARC EM9D 32-bit DSP Enhanced Processor core based on the ARCv2DSP ISA with CCM and XY Memory

- Dual 32x16 XMAC component supports up to two 32x16 MAC operations per instructions and supports all the 32x16 & dual 16x16 MAC instructions

- Dual XMAC built in shifters and 80-bit accumulators allow pseudo floating-point operations to be performed which greatly expanded dynamic range

- RAM configuration optimized for efficient area and power

- Improved system efficiency with enhanced ARM® AMBA® AXI™/AHB™ bus bridges

-

ARC EM11D Enhanced 32-bit processor core, ARCv2DSP ISA with Cache and XY Memory

- Dual 32x16 XMAC component supports up to two 32x16 MAC operations per instructions and supports all the 32x16 & dual 16x16 MAC instructions

- Dual XMAC built in shifters and 80-bit accumulators allow pseudo floating-point operations to be performed which greatly expanded dynamic range

- RAM configuration optimized for efficient area and power

- Improved system efficiency with enhanced ARM® AMBA® AXI™/AHB™ bus bridges

-

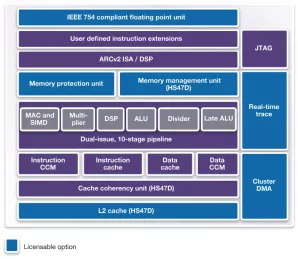

ARC HS47Dx4 quad-core version of dual-issue HS47D ARCv2DSP ISA, with 100+ DSP instructions and I&D cache

- Dual 32x16 XMAC component supports up to two 32x16 MAC operations per instructions and supports all the 32x16 & dual 16x16 MAC instructions

- Dual XMAC built in shifters and 80-bit accumulators allow pseudo floating-point operations to be performed which greatly expanded dynamic range

- RAM configuration optimized for efficient area and power

- Improved system efficiency with enhanced ARM® AMBA® AXI™/AHB™ bus bridges