DVB IP

Filter

Compare

135

IP

from

20

vendors

(1

-

10)

-

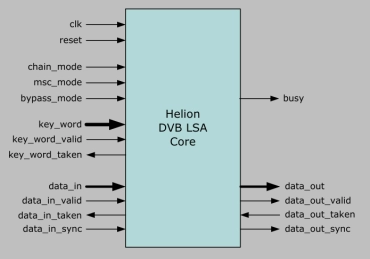

DVB Local Scrambling Algorithm Core

- The Helion DVB LSA Scrambler and Descrambler cores implement the Local Scrambling Algorithm as specified to provide MPEG-2 Transport Stream packet security within DVB Content Protection and Copy Management (DVB-CPCM) compliant systems.

- Both cores provide all operations required to scramble or descramble MPEG-2 TS packets, including IV generation using either MSC Data Independent (MDI) or MSC Data Dependent (MDD) mode, and payload protection using either AES-CBC or AES-RCBC cipher chaining modes.

-

DVB-S2 Demodulator

- Compliant with ETSI 302 307 V1.2.1 (2009-08) (DVB-S2)

- Supports CCM mode for broadcasting. ACM and VCM modes will be available soon

- Support for QPSK and 8-PSK modulations. 16-APSK and 32-APSK will be available soon

- Support for short blocks (16200 bits) and long blocks (64800 bits)

-

DVB-RCS2 Turbo Decoder

- Compliant with ETSI 301 545-2 V1.1.1 (2012-01) (DVB-RCS2)

- Support for all DVB-RCS2 payload

block sizes (14 to 599 bytes) and code rates (1/3 to 7/8) - Support for all modulation schemes

(QPSK, 8-PSK, 16-QAM)

-

DVB-S2 BCH and LDPC Encoder and Decoder

- Compliant with ETSI 302 307 V1.2.1 (2009-08) (DVB-S2).

- Support for short blocks (16200 bits) and long blocks (64800 bits).

- Support for all modulation schemes (QPSK, 8-PSK, 16-APSK, 32-APSK).

- Support for all interleaving schemes of all modulation schemes.

-

DVB Remultiplexer N-to-M

- Drop-in module for Spartan 6, Virtex-6, Artix-7, Kintex-7, Zynq FPGAs

- N SPI input / M SPI output (N and M from 1 to 8)

- Adapt one or several MPTS/SPTS stream into one or several MPTS by filtering and multiplexing complete services

- SFN MIP table insertion independent for each output (for DVB-T core control)

-

DVB-C Demodulator

- The demodulator is designed to be used together with a cable tuner and an analog to digital converter (ADC).

- The system has an internal state machine to control the operation, which can be externally configured via the SPI interface.

- This DVB-C QAM demodulator is supplied as a portable and synthesizable Verilog-2001 IP.

-

DVB-T2 Demodulator and LDPC/ BCH Decoder

- DVB-T2 EN302 755 V1.2.1, Rev.9 compliant

- Supports IF input

- Single input – Single output (SISO)

- Sampling frequency offset (SFO) tracking and compensation

- Carrier frequency offset (CFO) detection and correction

-

DVB-RCS2 Turbo Decoder and Encoder

- 16-state double binary turbo Encoder/Decoder.

- Puncturing/De-puncturing on the fly.

- Run time selectable number of iterations.

- Parallel decoding algorithm.

- Hard decision output.

-

DVB-S2 LDPC BCH Decoder and Encoder

- The DVB-S2 LDPC-BCH block is a powerful FEC (Forward Error Correction) subsystem for Digital Video Broadcasting via Satellite.

- In Digital video broadcasting for digital transmission for satellite applications, a powerful FEC sub-system is needed. FEC is based on LDPC (Low Density Parity Check) codes concatenated with BCH (Bose Chaudhuri Hocquenghem) codes, allowing Quasi Error Free operation close to the Shannon limit.