DDRn Controller IP

Filter

Compare

566

IP

from

62

vendors

(1

-

10)

-

SDRAM DDR Controller

- Dolphin Technology offers high performance DDR4/3/2 SDRAM and LPDDR5/4x/4/3/2 SDRAM Memory Controller IP across a broad range of process technologies.

-

DDR3 and DDR4 Controller and PHY on TSMC 12nm

- This DDR3/4 IP combo solution presented, is meticulously designed for high performance and low power consumption, utilizing sophisticated architecture and advanced technology.

- Fabricated in TSMC’s 12nm CMOS process, this solution includes both controller and PHY IPs, providing comprehensive support for DDR3 and DDR4 memory interfaces.

-

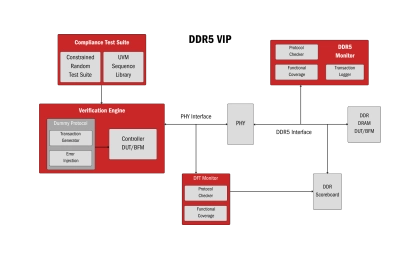

DDR5 Controller - Ensures high-speed, efficient operation and compatibility of memory controllers

- DDR5 Verification IP supports data rates up to 8400 MT/s, ensuring high-performance memory controllers meet the latest standards for speed, capacity, and power efficiency. It is designed to validate advanced features such as error correction and power management.

- This tool is ideal for validating DDR5 controllers in applications ranging from high-performance computing to mobile devices, ensuring robust performance and seamless integration in various systems

-

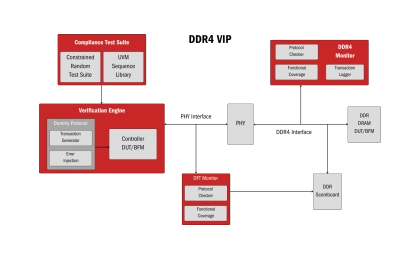

DDR4 Controller - Validates memory compliance, optimizes performance, ensures reliability

- The DDR4 Memory Controller Verification IP ensures compliance with DDR4 standards, validating high-speed data transfer, read/write operations, and error correction. It provides automated testing, advanced debugging tools, and scalability for complex memory systems.

- Designed for versatile applications, this IP optimizes performance in gaming consoles, data centers, AI systems, networking devices, and more. It ensures memory reliability, efficiency, and scalability across industries, accelerating time-to-market for DDR4-based products

-

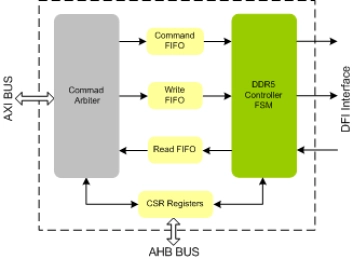

DDR5 Controller IIP

- Supports DDR5 protocol standard JESD79-5 and JESD79-5 Rev1.40 (Draft) Specification.

- Compliant with DFI version 5.0 Specification.

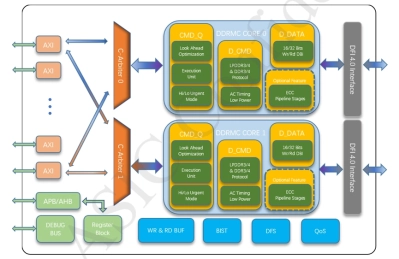

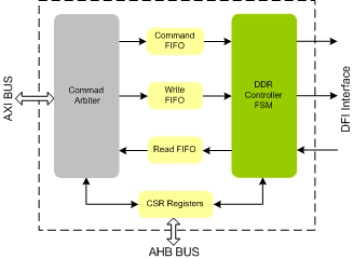

- Supports up to 16 AXI ports with data width upto 512 bits.

- Supports controllable outstanding transactions for AXI write and read channels

-

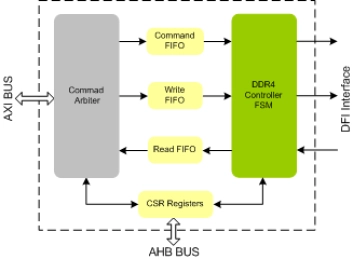

DDR4 Controller IIP

- Supports DDR4 protocol standard JESD79-4, JESD79-4A, JESD79-4A_r2, JESD79-4B, JESD79-4C and JESD79-4D (Draft) Specification.

- Compliant with DFI-version 3.0 or higher Specification.

- Supports up to 16 AXI ports with data width upto 512 bits.

- Supports controllable outstanding transactions for AXI write and read channels

-

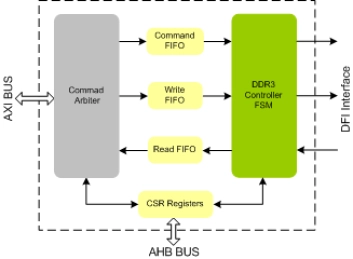

DDR3 Controller IIP

- Supports DDR3 protocol standard JESD79-3F Specification.

- Compliant with DFI-version 2.0 or higher Specification.

- Supports all the DDR3 commands as per the specs.

- Supports up to 16 AXI ports with data width upto 512 bits.

-

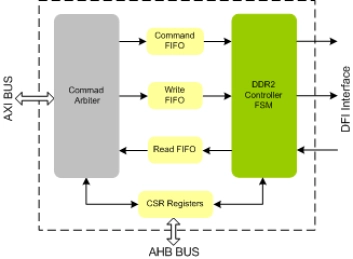

DDR2 Controller IIP

- Supports DDR2 protocol standard JESD79-2F Specification.

- Compliant with DFI-version 2.0 or higher Specification.

- Supports all the DDR2 commands as per the specs.

- Supports up to 16 AXI ports with data width upto 512 bits.

-

DDR Controller IIP

- Supports DDR protocol standard JESD79F Specification.

- Compliant with DFI-version 2.0 or higher Specification.

- Supports all the DDR commands as per the specs.

- Supports up to 16 AXI ports with data width upto 512 bits.

-

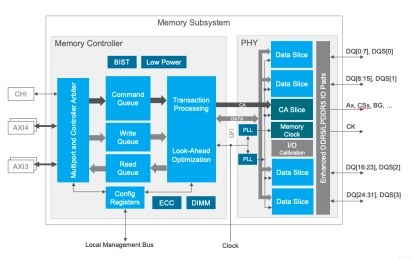

DDR Controller

- Sideband and in-line SEC/DED ECC

- Supports advanced RAS features including error scrubbing, parity, etc.

- Compliant to LPDDR5/4X/4/3 and DDR5/4/3 protocol memories

- Memory controller interface complies with DFI standards up to version 5.0

- Priority per command on Arm® AMBA® 4 AXI, AMBA 3 AXI

- Single and multi-port host interface options

- QoS features allow command prioritization on Arm AMBA 4 AXI and CHI interfaces

- Silicon proven and shipping in volume