DDR3 and DDR4 Controller and PHY on TSMC 12nm

This DDR3/4 IP combo solution presented, is meticulously designed for high performance and low power consumption, utilizing sophi…

Overview

This DDR3/4 IP combo solution presented, is meticulously designed for high performance and low power consumption, utilizing sophisticated architecture and advanced technology. Fabricated in TSMC’s 12nm CMOS process, this solution includes both controller and PHY IPs, providing comprehensive support for DDR3 and DDR4 memory interfaces. The DDR4 interface achieves speeds of up to 3200Mbps. Architecturally, it features a Multiport AMBA AXI interface, with configurable port numbers and support for both asynchronous and synchronous AXI ports. The PHY interface integrates a DFI 4.0 compatible design, with three embedded de-skew PLLs to enhance jitter performance.

Key features

- Support DDR4 up to 3200Mbps speed, DDR3 up to 2133Mbps

- Support Multiport AMBA AXI4 interface, port number, asynchronous or synchronous AXI port, data width, FIFO depth, and command queue depth configurable;

- Support DFI4.0 compliant interface between controller and PHY;

- Support 2 ranks, max density up to 8GB;

- Support automatic temperature monitor and refresh rate adjust;

- Support CA, write, read VREF eye training and per-bit de-skew training, write leveling training;

- Support Inline BIST and SIPI/LFSR/USER patterns;

- Support DDRPHY loopback test;

- Support fully pin-mux easy for PKG/PCB routing;

- Support mask write, write/read DBI;

- Support 2T CA timing, CA parity, and gear down mode; (DDR4)

- Support ECC (error correcting code), 32/64bit data+8bit ECC, correct 1bit-error and detect 2bit-error; (DDR4)

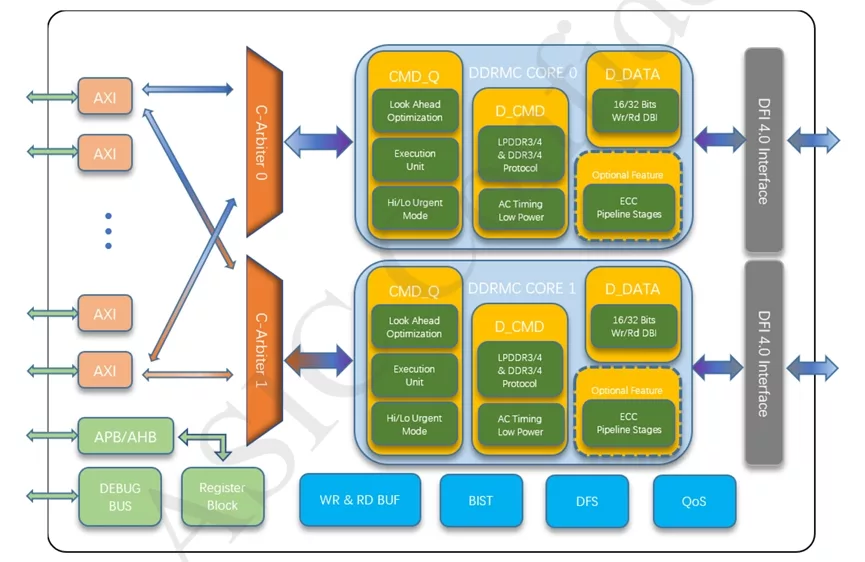

Block Diagram

Benefits

- Optimized for high bandwidth and low latency

- Suitable for high-performance, low-power SoC integration

- Simplifies DDR integration with pre-verified PHY and controller

- Reduced risk with built-in training, BIST, and loopback features

Applications

- AI SoC, Consumer Electronics, Networking, Industrial Control, Storage Controllers

What’s Included?

- Datasheet with integration guidelines

- Register Map, Timing Sheet

- Encrypted RTL + Netlist + Layout (.LEF, GDS, SDF)

- Verification environment & testbenches

- SDC constraints

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 12nm | FFC | Silicon Proven |

Specifications

Identity

Provider

Learn more about Single-Protocol PHY IP core

Design IP Faster: Introducing the C~ High-Level Language

Universal Flash Storage: Mobilize Your Data

Can MIPI and MDDI Co-Exist?

Enter the Inner Sanctum of RapidIO: Part 1

Networking software key to PICMG 2.16 optimization

Frequently asked questions about Single-Protocol PHY IP

What is DDR3 and DDR4 Controller and PHY on TSMC 12nm?

DDR3 and DDR4 Controller and PHY on TSMC 12nm is a Single-Protocol PHY IP core from Key ASIC listed on Semi IP Hub. It is listed with support for tsmc Silicon Proven.

How should engineers evaluate this Single-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Single-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.