DDR4 3 PHY IP

Filter

Compare

16

IP

from

3

vendors

(1

-

10)

-

DDR4 multiPHY in UMC (28nm)

- Low latency, small area, low power

- Compatible with JEDEC standard DDR4 up to 2667 Mbps

- Compatible with JEDEC standard DDR3 SDRAMs up to 2133 Mbps

- Compatible with JEDEC standard LPDDR2 SDRAMs up to 1066 Mbps

-

DDR4 multiPHY in TSMC (28nm)

- Low latency, small area, low power

- Compatible with JEDEC standard DDR4 up to 2667 Mbps

- Compatible with JEDEC standard DDR3 SDRAMs up to 2133 Mbps

- Compatible with JEDEC standard LPDDR2 SDRAMs up to 1066 Mbps

-

DDR4 multiPHY in Samsung (14nm)

- Low latency, small area, low power

- Compatible with JEDEC standard DDR4 up to 2667 Mbps

- Compatible with JEDEC standard DDR3 SDRAMs up to 2133 Mbps

- Compatible with JEDEC standard LPDDR2 SDRAMs up to 1066 Mbps

-

DDR5/DDR4 and LPDDR5/LPDDR4 EMIF FPGA IP

- DDR4 and DDR5 offer higher bandwidth and improved performance over previous generations, with DDR5 providing further enhancements in speed and power efficiency

- LPDDR4 and LPDDR5 are optimized for low power consumption, making them ideal for embedded applications, with LPDDR5 offering even faster data rates and improved energy management

- When integrated with Altera FPGAs these memory technologies enable faster data processing and more efficient power usage for a wide range of applications including networking, cloud and edge.

-

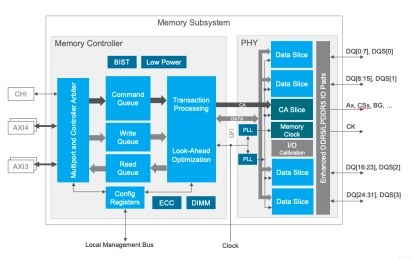

DDR Controller

- Sideband and in-line SEC/DED ECC

- Supports advanced RAS features including error scrubbing, parity, etc.

- Compliant to LPDDR5/4X/4/3 and DDR5/4/3 protocol memories

- Memory controller interface complies with DFI standards up to version 5.0

- Priority per command on Arm® AMBA® 4 AXI, AMBA 3 AXI

- Single and multi-port host interface options

- QoS features allow command prioritization on Arm AMBA 4 AXI and CHI interfaces

- Silicon proven and shipping in volume

-

LPDDR4 multiPHY V2 in UMC (28nm)

- Low latency, small area, low power

- Compatible with JEDEC standard LPDDR4 SDRAMs up to 4,267 Mbps

- Maximum data rate is process technology dependent

- Compatible with JEDEC standard DDR4 SDRAMs up to 3,200 Mbps

-

LPDDR4X multiPHY Plus in GF (12nm)

- Low latency, small area, low power

- Compatible with JEDEC standard LPDDR4 SDRAMs up to 4,267 Mbps

- Maximum data rate is process technology dependent

- Compatible with JEDEC standard DDR4 SDRAMs up to 3,200 Mbps

-

LPDDR4X multiPHY in TSMC (16nm) for Automotive

- Low latency, small area, low power

- Compatible with JEDEC standard LPDDR4 SDRAMs up to 4,267 Mbps

- Maximum data rate is process technology dependent

- Compatible with JEDEC standard DDR4 SDRAMs up to 3,200 Mbps

-

LPDDR4X multiPHY in GF (14nm)

- Low latency, small area, low power

- Compatible with JEDEC standard LPDDR4 SDRAMs up to 4,267 Mbps

- Maximum data rate is process technology dependent

- Compatible with JEDEC standard DDR4 SDRAMs up to 3,200 Mbps

-

LPDDR4X multiPHY in Samsung (14nm, 11nm)

- Low latency, small area, low power

- Compatible with JEDEC standard LPDDR4 SDRAMs up to 4,267 Mbps

- Maximum data rate is process technology dependent

- Compatible with JEDEC standard DDR4 SDRAMs up to 3,200 Mbps