C-PHY / D-PHY Combo IP

Filter

Compare

60

IP

from

11

vendors

(1

-

10)

-

MIPI C-PHY v2.0 /D-PHY v2.5 Combo IP in TSMC

- Compliant with MIPI D-PHY spec up to v2.5 and C-PHY spec up to v2.0

- Support both MIPI DSI and CSI-2 protocols

-

MIPI C-PHY℠ v2.0 + D-PHY℠ v2.5 Combo IP Core

- This Tx/Rx transceiver complies with the MIPI Alliance C-PHY℠ v2.0 and D-PHY℠ v2.5 specifications, with world-class area and power dissipation, and is available for a range of foundry processes.

- This IP delivers 6 Gbps per lane for a max throughput of 24 Gbps in D-PHY℠ mode, and 6 Gsps per trio for a max throughput of 41.04 Gbps in C-PHY℠ mode.

-

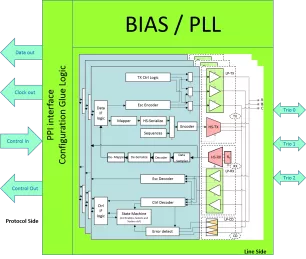

MIPI C-PHY/D-PHY Combo IP

- The MIPI C/D-PHY combo IP is a high-frequency low-power, low cost, physical layer compliant with the MIPI® Alliance Standard for C-PHY and D-PHY.

- The PHY can be configured as a MIPI Master or MIPI Slave, supporting camera interface CSI-2 v1.2 or display interface DSI v1.3 applications in the D-PHY mode. It also supports camera interface CSI-2 v1.3 and display interface DSI-2 v1.0 applications in the C-PHY mode.

-

MIPI C/D Combo TX PHY and DSI controller

- High Data Rates: Supports data transmission rates

- Energy Efficiency: Optimized for low power consumption, making it ideal for battery-powered devices

- Complete Solution: Combines the MIPI CD-PHY Transmitter PHY and DSI Controller to make it a one-stop solution

- Flexible IP Configuration

-

MIPI DSI-2 High Performance Device Combo Controller for Automotive

- Compliant with the MIPI DSI and DSI-2 specifications, v2.1

- Support for dual MIPI DSI use case with VESA Display Stream Compression (DSC) v1.1 standard

- Support for video and command modes

- Wide PPI interface to C-PHY v1.2 and D-PHY v2.1

-

MIPI DSI-2 High Performance Device Combo Controller

- Compliant with the MIPI DSI and DSI-2 specifications, v2.1

- Support for dual MIPI DSI use case with VESA Display Stream Compression (DSC) v1.1 standard

- Support for video and command modes

- Wide PPI interface to C-PHY v1.2 and D-PHY v2.1

-

MIPI DSI Host Combo Controller

- Compliant with the MIPI DSI and DSI-2 specifications, v2.1

- Support for dual MIPI DSI use case with VESA Display Stream Compression (DSC) v1.1 standard

- Support for video and command modes

- Wide PPI interface to C-PHY v1.2 and D-PHY v2.1

-

MIPI CSI-2 High Performance Host Controller Combo ASIL Compliant

- Supports key features of the latest MIPI CSI-2 specification

- PPI interface to MIPI C-PHY v1.2 and D-PHY v2.1

- Programmable multi-lane merging

- Short and long packet format and all primary and secondary CSI-2 data formats

-

MIPI CSI-2 High Performance Host Controller Combo

- Supports key features of the latest MIPI CSI-2 specification

- PPI interface to MIPI C-PHY v1.2 and D-PHY v2.1

- Programmable multi-lane merging

- Short and long packet format and all primary and secondary CSI-2 data formats

-

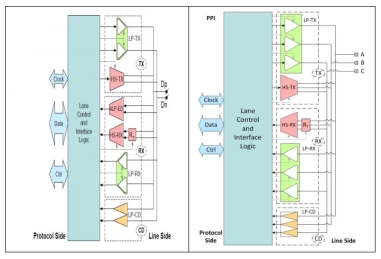

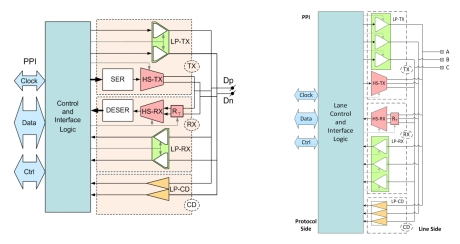

MIPI C/D Combo PHY RX - GlobalFoundries 22FDX

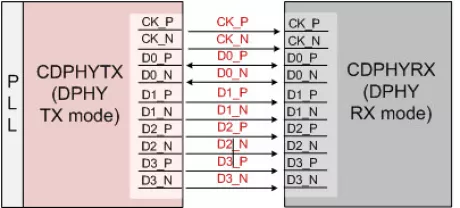

- Supports up to one clock lane and four data lanes for DPHY1.2

- Fully compliant with MIPI D-PHY v1.2 and C-PHY v1.0 spec

- Available in GlobalFoundries 22FDX process

- Three 3phase encoded data lanes for CPHY1.0