Analog / Mixed-Signal IP

Filter

Compare

86

IP

from

16

vendors

(1

-

10)

-

Analog I/O Library with a custom 12V ESD Solution IN GF 55nm

- This I/O library is a silicon-proven, flip-chip-optimized analog and mixed-signal I/O Library for GlobalFoundries 55nm BCD technology.

- It provides a comprehensive set of 1.8V, 3.3V, 5V, and 12V analog I/O and power pads, designed for robust ESD protection, flexible pad-ring construction, and reliable operation across industrial temperature ranges.

-

Specialed 20V Analog I/O in TSMC 55nm

- A TSMC 55nm LP Specialized 20V Analog I/O in Standard Low Voltage CMOS

- This silicon-proven TSMC 55nm LP 20V ESD cell is a high-voltage electrostatic discharge (ESD) protection solution specifically engineered forlow-power and high-performance applications.

- This ESD cellis designed to safeguard high- voltage interfaces commonly found in analog, mixed-signal, RF, and power management ICs, where protection against electrostatic discharge events is critical for long-term reliability.

-

Complete measurement analog front end (AFE) IP for single phase power metering

- Embedded Computation Engine for utility billing applications

- Low noise Programmable Gain Amplifier (PGA), to reach the best class accuracy with each type of sensors

- Embedded power management for the best resilience to power supply noise

-

Complete measurement analog front end (AFE) IP for single phase power metering

- Embedded Computation Engine for utility billing applications

- Low noise Programmable Gain Amplifier (PGA), to reach the best class accuracy with each type of sensors

- Embedded power management for the best resilience to power supply noise

-

Complete measurement analog front end (AFE) IP for three-phase power metering

- Embedded Computation Engine for utility biling applications

- Low noise Programmable Gain Amplifier (PGA), to reach the best class accuracy with each type of sensors

- Embedded power management for the best resilience to power supply noise

-

Complete measurement analog front end (AFE) IP for three-phase power metering

- Embedded Computation Engine for utility billing applications

- Low noise Programmable Gain Amplifier (PGA), to reach the best class accuracy with each type of sensors

- Embedded power management for the best resilience to power supply noise

-

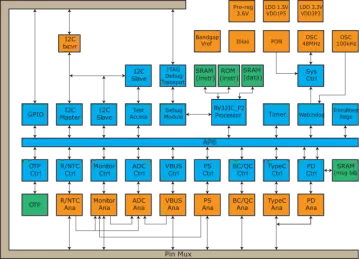

Digital and mixed-signal IP and ASIC RISC-V reference design for USB Type-C/PD power adapter/charger

- RISC-V RV32EC processor subsystem with debug module, JTAG debug transport, and instruction and data ROM and SRAMs

-

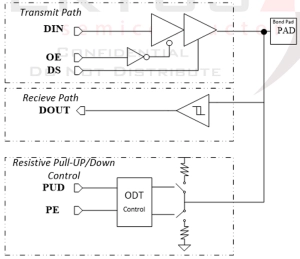

1.8V GPIO, 1.8V & 3.3V Analog in TSMC 180nm BCD

- The silicon-proven I/O library in TSMC 180nm BCD provides a reliable and flexible solution for mixed-signal, power management, and BCD applications.

- The library includes a 1.8V digital I/O cell, optimized for up to 100MHz operation at 15pF, ensuring efficient high-speed performance.

- It also features 1.8V and 3.3V baseline analog I/Os, along with custom low-leakage 3.3V analog I/Os, tailored for low-power and precision-driven designs.

-

24-bit Cap-less ADC with 101 dB SNR, offering low power consumption and low latency, supporting 1 channel (mono) in TSMC 12FFC+

- mADC101-SW3-FF.01 is a mixed-signal (analog and digital) virtual component in TSMC 12FFC+ that includes a single mono ADCs and additional functions, making it an ideal front-end for low power, fast wake-up, and high-quality audio applications.

- It also features ultra-low latency capability for ANC applications.

-

NVM MTP EEPROM TSMC 65nm LP 2.5V SVT, SVT/HVT

- Synopsys MTP EEPROM Non-Volatile Memory (NVM) IP is a Multi-Time Programmable (MTP) block developed in standard logic CMOS processes

- Supporting up to 8-Kbit configurations and up to 400,000 write cycles with program/erase and read operations up to 125°C, the compact NVM IP enables true electrically erasable programmable read only memory (EEPROM) performance without requiring additional masks for processing steps

- Delivered as a hard IP block, the low-power, reprogrammable Synopsys MTP EEPROM NVM IP operates from the core supply and includes all the necessary support and control circuitry, including all high-voltage generation and distribution required for programming

- Synopsys MTP EEPROM NVM IP is available in advanced, high voltage, BCD, and analog mixed-signal processes.