ASIL-D safety IP

Filter

Compare

10

IP

from

5

vendors

(1

-

10)

-

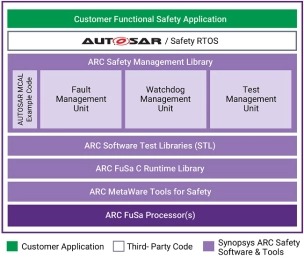

ARC Functional Safety Software

- The functional safety (FuSa) software components in conjunction with Synopsys’ ASIL certified MetaWare Development Tools for Safety and industry leading ARC® FS processors provide comprehensive ASIL compliant solutions which dramatically reduce customers’ risk and SoC certification effort.

-

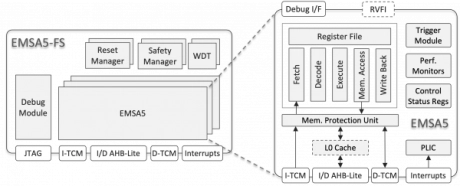

32-bit Embedded RISC-V Functional Safety Processor

- The EMSA5-FS is a processor core designed for functional safety.

- The fault-tolerant processor uses dual or triple instances of the EMSA5, an efficient 32-bit embedded processor IP core implementing the RISC-V Instruction Set Architecture (ISA).

-

Functional-Safety & Secure LPDDR3 Memory Subsystem

- Safe & Secure-LPDDR3 that is ready for ASIL (Automotive Safety Integrity Level) and secure by design

- Functional Safety out-of-the box design, with an extensive ASIL documentation package.

- Integrated security features into the controller. Characterized for extended operating conditions and long-term reliability.

-

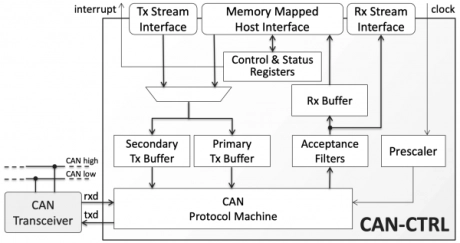

CAN CC, CAN FD, and CAN XL Bus Controller

- The CAN-CTRL implements a highly featured and reliable CAN bus controller that performs serial communication according to the Controller Area Network (CAN) protocol.

- It supports classical CAN and CAN FD according to ISO 11898-1:2015; CAN XL as specified in CiA 610-1 specification; Time-Triggered CAN (TTCAN) per ISO 11898-4; and CAN Frame time-stamping as described in the CiA 603 profile.

- This CAN controller core handles data rates exceeding 20Mbit/s and it is optimized for the AUTOSAR and SAE J1939 specifications.

-

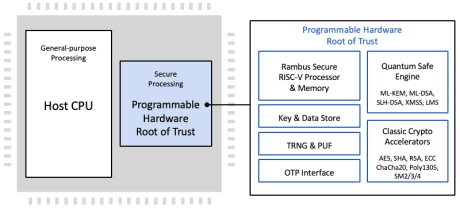

Quantum Safe, ISO 21434 Automotive-grade Programmable Hardware Security Module

- The automotive-grade CryptoManager RT-7xx v3 Root of Trust family is the next generation of fully programmable ISO 26262 and ISO 21434 compliant hardware security modules offering Quantum Safe security by design for secure automotive applications.

- The CryptoManager RT-7xx family protects against a wide range of hardware and software attacks through state-of-the-art side channel attack countermeasures and anti-tamper and security techniques.

-

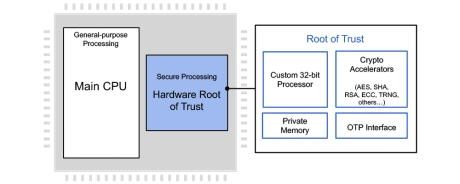

Embedded Hardware Security Module (Root of Trust) - Automotive Grade ISO 26262 ASIL-B

- The RT-64x Embedded Hardware Security Module (Root of Trust) family are fully programmable, ISO 26262 ASIL-B hardware security cores offering security by design for automotive applications.

- They protect against a wide range of failures such as permanent, transient and latent faults and hardware and software attacks with state-of-the-art anti-tamper and security techniques.

-

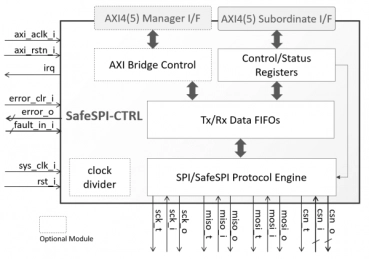

SafeSPI Controller

- The SafeSPI-CTRL implements a versatile and highly reliable Serial Peripheral Interface (SPI) controller compliant with the SafeSPI specification.

- Offering maximum flexibility to the host system, a single instance of the SafeSPI-CTRL can be programmed to act as a SafeSPI master, slave, or monitor, or as master or slave controller for conventional SPI.

-

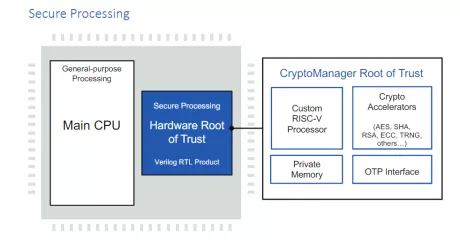

Embedded HSM Family (Root of Trust) - Automotive Grade ISO 26262 ASIL-B

- Custom-designed 32-bit RISC-V secure processor

- Security model include hierarchical privilege model, secure key management policy, hardware-enforced isolation/access control/protection, error management policy

- Standard hardware cryptographic accelerators, including AES (all modes), HMAC, SHA-2 (all modes), RSA up to 4096 bits, ECC up to 521 bits, a NIST-compliant Random Bit Generator, AXI Multi Issue Out-of-Order, and Fast DMA capability. Additional algorithms such as Whirlpool (SHE), SHA-1 (legacy), AES-CMAC, SHA-3, Poly1305, ChaCha and OSCCA SM2-3-4 are available

- Multi-layered security model protects all core components against a wide range of attacks

-

IP for Automotive Applications

- Comprehensive automotive Interface and Foundation IP.

- IP must achieve ASIL-B level functional safety certification.

- IP must meet AEC-Q100 standard reliability.

-

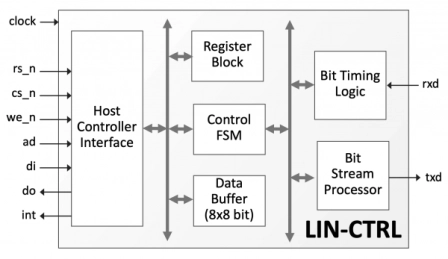

LIN Bus Master/Slave Controller

- Support of LIN specifications 2.0, 2.1, and 2.2A

- Backward compatible with LIN specification 1.3

- Run-time configurable master or slave operation

- Programmable data rate between 1 Kbit/s and 20 Kbit/s (for master)