ARINC 429 IP

Filter

Compare

15

IP

from

10

vendors

(1

-

10)

-

ARINC 429 IP

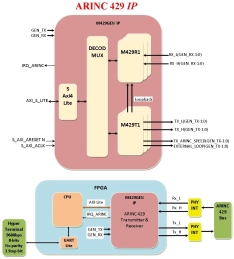

- The M429GEN IP implements a synchronous single-chip ARINC 429 Transmit and Receive Controller capable of linking one CPU to one or several ARINC 429 bus.

- The IP controls all ARINC 429 bus specific sequences, protocol and timing. The M429GEN IP interface allows the parallel-bus microprocessor to communicate bidirectionally with the ARINC 429 bus.

-

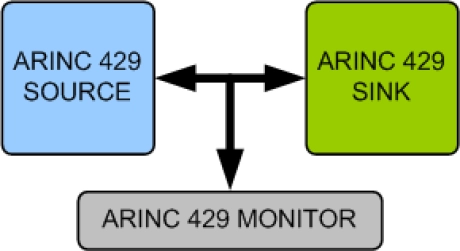

ARINC 429 Verification IP

- Supports ARINC SPECIFICATION 429 PART 1-17.

- Supports all word structures and protocol necessary to establish bus communication as per the specs.

- Supports simplex, twisted shielded pair data bus standard Mark 33 Digital Information Transfer System bus.

- Supports LRU with multiple transmitters and receivers communicating on different buses.

-

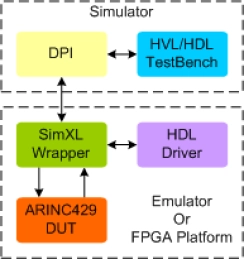

ARINC 429 Synthesizable Transactor

- Supports ARINC SPECIFICATION 429 PART 1-17

- Supports all word structures and protocol necessary to establish bus communication as per the specs

- Supports simplex, twisted shielded pair data bus standard Mark 33 Digital Information Transfer System bus

- Supports LRU with multiple transmitters and receivers communicating on different buses

-

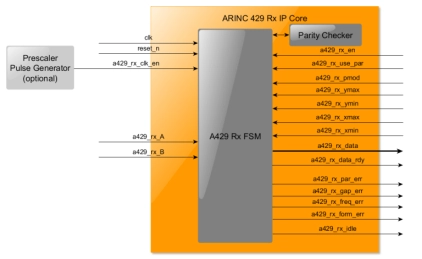

ARINC 429 IP Core

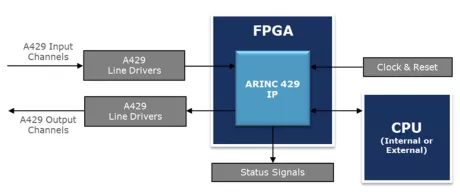

- Implements ARINC 429 Data Bus Communication Protocol.

- Supports both Transmit and Receive functionality for ARINC 429 words.

- Configurable data rates for flexible integration into avionics systems.

- Provides advanced error detection mechanisms for high data integrity.

- Bare-metal application or PetaLinux OS with associated APIs.

-

ARINC 429 IP Core

- ARINC 429 IP Core implements ARINC 429 standard.

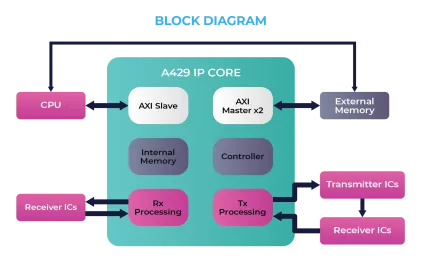

- IP Core contains Rx and Tx processing blocks, Controller Block, Internal Memory and External Memory Interfaces.

- A429 IP communicates with CPU (Central Processing Unit) and external memory through AXI interface.

-

ARINC 429 IP-Core with DO-254 Package

- Applicable Standards:

- Configuration support per channel:

- Technical features:

- Supported tools:

-

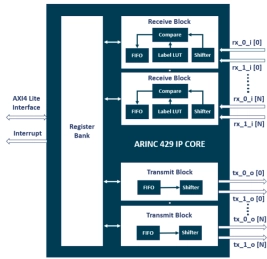

ARINC 429 IP Core

- Multichannel module supporting ARINC429 Receiver/Transmitter.

- Configurable module supporting any number of receivers and transmitters (Standard with 16 receivers & 8 transmitters).

- Configurable data rate supporting from 12.5 Kbps to 1 Mbps.

- Parity & Gap generators & checkers for high data integrity.

-

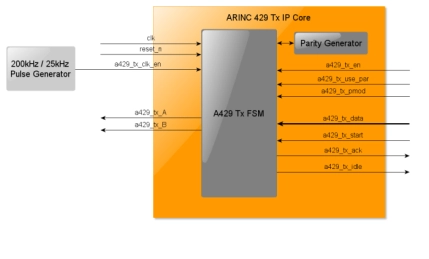

ARINC 429 Transmitter DO-254 IP Core

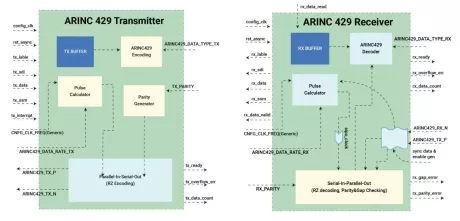

- The ARINC 429 Tx IP Core implements a transmitter as specified in the ARINC Specification 429 Part 1-17.

- The ARINC 429 Rx Core has been developed to DAL A according to the DO-254 / ED-80 and is accompanied by a Certification Kit.

-

ARINC 429 Receiver DO-254 IP Core

- Design Assurance Level A according to RTCA DO-254/ED-80 (April, 2000)

- Fully compliant to Bosch’s CAN Specification 2.0 (Sep 1991)

- Time Triggered Communication (TTC) support according to ISO 11898-1 (2003-12-01)

- Tested as specified in the ISO 16845 (2004-03-15)

-

ARINC 429 Tx & Rx

- User ARINC 429 configuration

- Programmable data rate for 100 kbsor 12.5kbs

- Transmitter and Receiver can b eEnabled /Disabled

- Based on vendor and technology independent VHDL code