ARINC 429 IP-Core with DO-254 Package

The ARINC-429 IP Core is a multi-channel ARINC 429 transmitter and receiver core for serial communication in airborne application…

Overview

The ARINC-429 IP Core is a multi-channel ARINC 429 transmitter and receiver core for serial communication in airborne applications. The IP is developed, validated & licensed by Oxytronic.

This IP Core has been developed according to the RTCA/DO-254 ED-80 guidelines. These guidelines are required by the Airworthiness Certification Authorities (EASA and FAA) for hardware developments that need to be certified for the use in commercial aircraft equipment.

The IP Core incorporates various state-of-the-art CPU interfaces which can easily be connected to your required interface. Each individual channel can be configured according to your specifications.

Each channel contains a specific buffer (FIFO), incorporated in the IP. This allows efficient data transfer between CPU and the IP.

Key features

- Applicable Standards:

- Supports ARINC 429 standard part 1, 2 and 3

- Developed according to RTCA/DO-254 ED-80 guidance (DAL-A to DAL-D criteria)

- Configuration support per channel:

- Low speed (LS, 12.5 kHz) or high speed (HS, 100 kHz) mode

- Disable/Enable

- Programmable Overflow, Parity, Frame error bits

- Programmable interrupts on Rx and Tx

- Configurable memory for Labels management

- Technical features:

- Supported CPU interfaces: AMBA AXI4Lite, Avalon, asynch. or customizable interface

- Flexible architecture allowing from 1 Rx and 1 Tx to unlimited number of Rx and Tx

- Independent channel configuration via the CPU interface

- 63 word buffer (FIFO) for each ARINC 429 input channel

- 31 word buffer (FIFO) for each ARINC 429 output channel

- Provided with a full-automated test bench with 100% code coverage

- Supported tools:

- Xilinx ISE & Vivado

- Microsemi Libero

- Altera Quartus

- Mentor Graphics ModelSim, Questa

- Cadence

- Synopsys Synplify

- Available Platforms:

- Microsemi FPGA & SoC

- Altera FPGA & SoC

- Xilinx FPGA & SoC

- ASIC technology

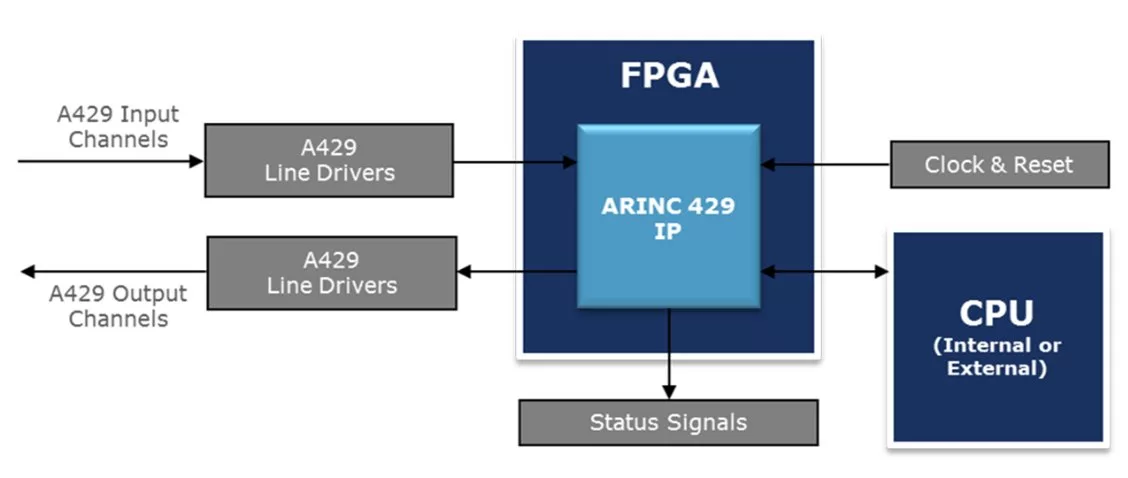

Block Diagram

Benefits

- Improved development flow several times already. Certified up to Level-A

- Flexible architecture allowing from 1 Rx and 1 Tx to unlimited number of Rx and Tx

- Rx-Tx channels easily configurable for other next use

- Effortlessly customizable Synchronous CPU interface

- Adaptable independent word buffers for each input or output channel

- Independent Channel parameterizations through CPU interface

- High speed and low speed mode configurability

- Exchange FIFO errors information available

- Silicon proven solution

Applications

- The IP is derived from ARINC-429 modules that have been integrated in at least 3 different types of cockpit video displays, implemented in different FPGAs, for which some displays were granted for TSO and ETSO certification (DAL-A and DAL-B).

What’s Included?

- Basic deliverables

- Datasheet

- IP ARINC-429 Netlist

- Functional verification test bench obtaining 100% code coverage

- Simulation and implementation scripts and logs in order to regenerate the same functional behavior

- Implementation results

- Deliverables for RTCA/DO-254 certification

- VHDL RTL sources compliant to the Oxytronic coding standard

- Delivered Documents (part of the IP package deliverables):

- Certification Liaison Process

- Plan for Hardware Aspect of Certification (PHAC)

- Hardware Accomplishment Summary

- Hardware Planning Process

- Hardware Development Plan

- Hardware Validation and Verification Plan (HVVP)

- Configuration Management Plan

- Hardware Process Assurance Plan

- Hardware Development Process

- Requirements capture

- Conceptual design data

- Detailed design data

- Hardware Verification and Validation Process

- Traceability Matrices

- Hardware Verification Procedures

- Verification Reports

- Hardware Configuration Management Process

- Hardware Configuration Index

- Hardware Environment Configuration Index

- Hardware Process Assurance Process

- Audit report

- Records

- Available Documents (for audit purpose only, not part of the IP package deliverables):

- Hardware Verification and Validation Process

- All reviews, audits and corresponding checklists

- Certification Liaison Process

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about ARINC 429 IP core

IP Based System Design for Aerospace and Military - The Time is Now

Embedded Systems -> RTOSes shield from net-centric bugs

Frequently asked questions about ARINC-429 IP cores

What is ARINC 429 IP-Core with DO-254 Package?

ARINC 429 IP-Core with DO-254 Package is a ARINC 429 IP core from Oxytronic listed on Semi IP Hub.

How should engineers evaluate this ARINC 429?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this ARINC 429 IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.