AES-GCM IP

Filter

Compare

98

IP

from

18

vendors

(1

-

10)

-

AES-XP-GCM Ultra-High-Performance Secure Core - Ultra-High-Performance AES-GCM Core with RAMBAM-Based SCA/FI Protection

- Ultra-High-Performance AES-GCM Core with RAMBAM-Based SCA/FI Protection

-

AES-GCM, Extreme-Speed IP Cores for AES256-GCM Authenticated Encryption

- High Security

- Extremely High Throughput

- Constant Latency

-

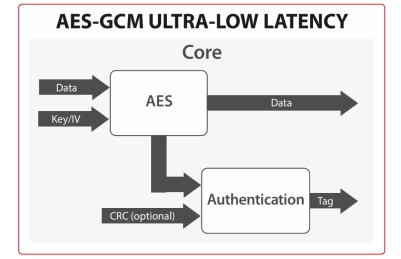

AES-GCM Ultra-low latency crypto engine

- The AES-GCM Ultra-low latency crypto engine is targeted for CXL link encryption with an implementation of the AES-GCM algorithm compliant with the NIST SP 800-38D standard.

- The unique architecture enables high throughput while maintaining an optimal resource usage.

-

AES-GCM, Advanced Encryption Standard (256-bit key), Galois Counter Mode IP Core

- Moderate resource requirements: The entire XIP1111H requires approximately 21700 Adaptive Lookup Modules (ALMs) (Intel ® Cyclone ® V), and does not require any multipliers, DSPBlocks or internal memory in a typical FPGA implementation. Contact sales@xiphera.com for ASIC resource requirements.

- Optimized Implementation utilizing unrolling, pipelining, optimized AES S-box design, and GMAC calculation based on pipelined Karatsuba multipliers enable extremely high performance.

- Performance: XIP1113H achieves a throughput in the tens of Gbps range, for example 65+ Gbps in Xilinx ® UltraScale+ MPSoC.

- Standard Compliance: XIP1113H is fully compliant with both the Advanced Encryption Algorithm (AES) standard, as well as with the Galois Counter Mode (GCM) standard.

-

AES-GCM, Advanced Encryption Standard (256-bit key), Galois Counter Mode IP Core

- Compact resource requirements: The entire XIP1113B requires less than 2800 Adaptive Lookup Modules (ALMs) (Intel® Cyclone®V), and does not require any multipliers, DSPBlocks or internal memory in a typical FPGA implementation. Contact sales@xiphera.com for ASIC resource requirements.

- Performance: Despite its compact size, XIP1113B achieves a throughput in the Gbps range, for example 2.0 Gbps in Xilinx® Artix®-7 family.

- Standard Compliance: XIP1113B is fully compliant with both the Advanced Encryption Algorithm (AES) standard, as well as with the Galois Counter Mode (GCM) standard.

- Test Vector Compliance: XIP1111B passes all test vectors specified in MACsec GCM-AES Test Vectors.

-

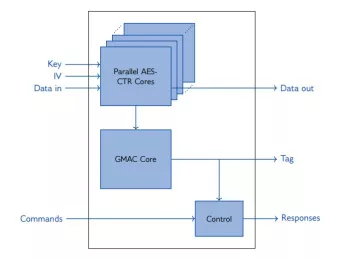

AES-GCM Encryption Core

- Full Verilog core

- Synth-time selectable number of parallel paths allows the user to balance area/bandwidth requirements

- Synth-time selectable internal buffer sizing for area/bandwidth balancing

- Synth-time selectable 128 or 256 bit AES encryption key size

-

AES-GCM Multi-channel upto 2Tbps Crypto Accelerator

- EXAMPLE CONFIGURATIONS

- The SafeXcel-IP-63 has a scalable number of processing pipes and channels. It is available in different configurations, suitable for different applications to meet different gate count and throughput objectives.

- • EIP-63a-c17-r

- o single pipe, 17 channels, register based (no memories)

-

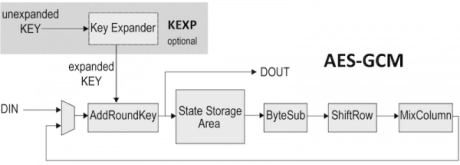

AES-GCM Authenticated Encrypt/Decrypt Engine

- Encrypts and decrypts using the AES Rijndael Block Cipher Algorithm

- NIST-Validated

- Implemented according to the National Institute of Standards and Technology (NIST) Special Publication 800-38D

- Processes 128-bit data in 32-bit blocks

-

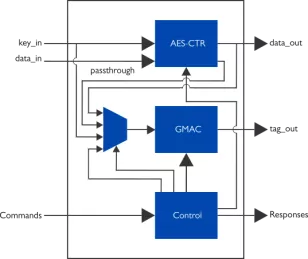

Ultra high performance AES-GCM for OTN networks

- Cipher Modes: AES-GCM (as specified in NIST SP800-38D)

- Compute Units: Selectable between 1, 2, 4, 8 or 16

-

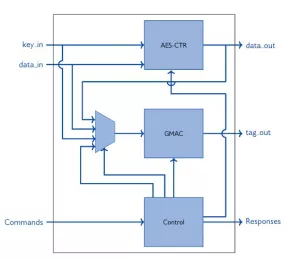

AES-GCM IP Core for 40Gbit/sec packet data

- Cipher Modes: AES-GCM as specified for 802.1ae MACSEC

- Internal Data Path Width: 128 bits with pipelining and overlapping

- Functions: Encrypt, Decrypt, Encrypt/Decrypt

- Key Lengths: 128 bits