5G IP

Filter

Compare

335

IP

from

75

vendors

(1

-

10)

-

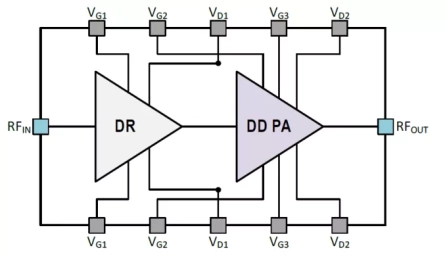

39GHz High-Efficiency CMOS Power Amplifier for 5G mmWave Applications

- 2-stage PAEmax = 45%

- PA-stage DEmax = 54%

- Psat = 18.3dBm

- Gain = 19dB

- Efficiency maintained at lower supply voltages for added reliability

-

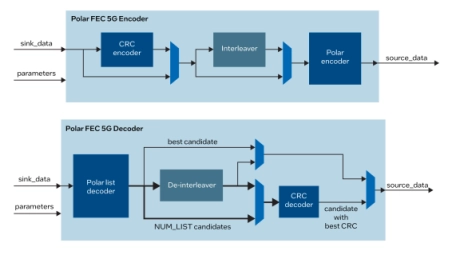

5G Polar Intel® FPGA IP

- The 5G Polar Intel® FPGA IP implements a forward error correction (FEC) encoder and decoder based on polar codes compliant with the 3rd Generation Partnership Project (3GPP) 5G specification for integration into your wireless design

- Polar codes represent an emerging class of error correction supporting the high throughput requirements for 5G new radio (NR).

-

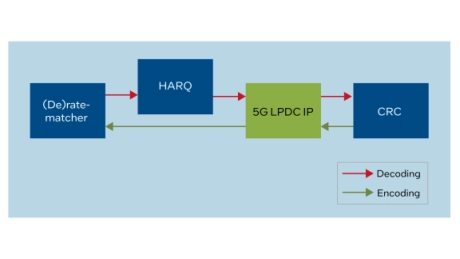

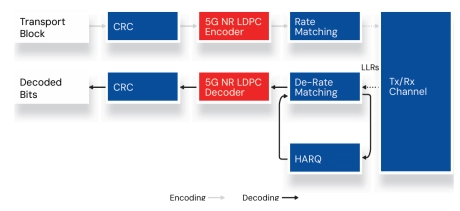

5G LDPC Intel® FPGA IP

- Low-density parity-check (LDPC) codes are linear error correcting codes that help you to transmit and receive messages over noisy channels

- The 5G LDPC and LDPC-V Intel® FPGA IP implement LDPC codes compliant with the 3rd Generation Partnership Project (3GPP) 5G specification for integration in your wireless design.

- LDPC codes offer better spectral efficiency than Turbo codes and support the high throughput for 5G new radio (NR).

-

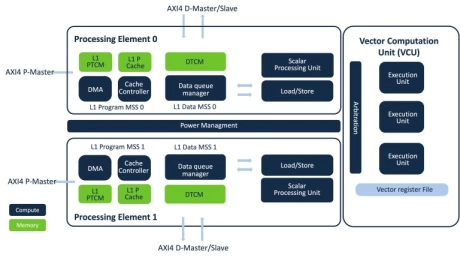

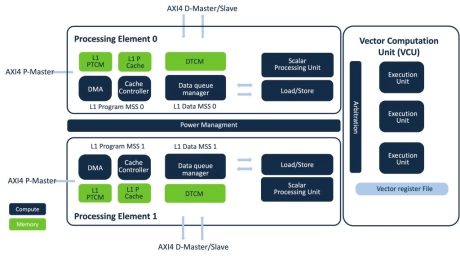

5G IoT DSP

- The XC21 is the most efficient vector DSP core available today for communications applications.

- The XC21 DSP is designed for low-power, cost- and size-optimized cellular IoT modems, NTN VSAT terminals, eMBB and uRLLC applications.

- Ceva-XC21 offers scalable architecture and dual thread design with support for AI, addressing growing demand for smarter, yet more cost and power efficient cellular devices

-

5G RAN DSP

- The XC23 is the most powerful DSP core available today for communications applications. The-XC23 offers scalable architecture and dual thread design with support for AI, addressing growing demand for smarter, more efficient wireless infrastructure

- Targeted for 5G and 5G-Advanced workloads, the XC23 has two independent execution threads and a dynamic scheduled vector-processor, providing not only unprecedented processing power but unprecedented utilization on real-world 5G multitasking workloads.

-

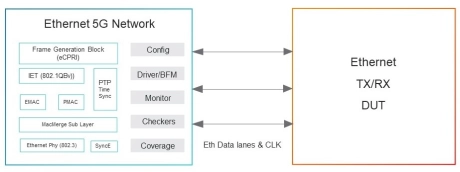

Simulation VIP for Ethernet 5G Network

- SyncE

- Supports clock generation from transmit side

- Supports Hold-off and Wait-to-restore feature

- Support for 25G speed with serial interface

-

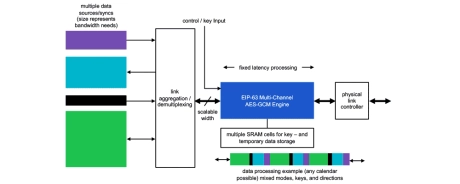

Inline cipher engine for PCIe, CXL, NVMe, 5G FlexE link integrity and data encryption (IDE) using AES GCM mode

- The ICE-IP-63 (EIP-63) is a scalable high-performance, multi-channel cryptographic engine that offers AES-GCM operations as well as AES-CTR and GMAC on bulk data.

- Its flexible data path is suitable to scale from 100 Gbps to 2.4 Tbps to provide a tailored engine with minimal area for your application.

- The FIFO-like data interface makes it possible to perform frame processing for many different protocols, including MACsec, IPsec, and OTN security.

-

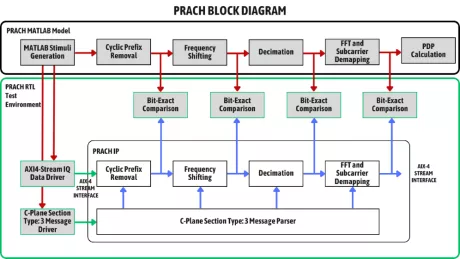

Optimize your 5G NR O-RAN Split 7.2X design with EIC cutting-edge PRACH Design and Verification Suite

- Comprehensive Support: All PRACH formats and configuration indexes described in 3GPP 38.211 are fully supported.

- Versatile Sequences: Length-139 and length-839 sequences are included.

- Frequency Multiplexing: Capable of decoding up to 8 frequencies multiplexed PRACHs.

-

LDPC Decoder for 5G NR and Wireless

- The 5G NR LDPC Decoder IP Core offers a robust solution for LDPC decoding, featuring a dedicated LDPC decoder block for optimal performance.

- It employs the Min-Sum LDPC decoding algorithm to ensure efficient decoding.

- The core allows for programmable internal bit widths at compile time, though the default values are usually sufficient.

-

NR-5G Polar Decoder and Encoder

- The Forward Error Correction (FEC) sub-system is one of the essential basing blocks in any communication systems so a powerful FEC code is needed.

- The New Radio (NR) FEC for the control channel is proposed to be designed based on Polar codes allowing close to the Shannon limit/Capacity operation.

- The Polar code successive cancellation decoding process as needed for 3GPP physical layer standard.