Cellular IoT and LPWAN - addressing the industry FUD

Chet Babla, ARM

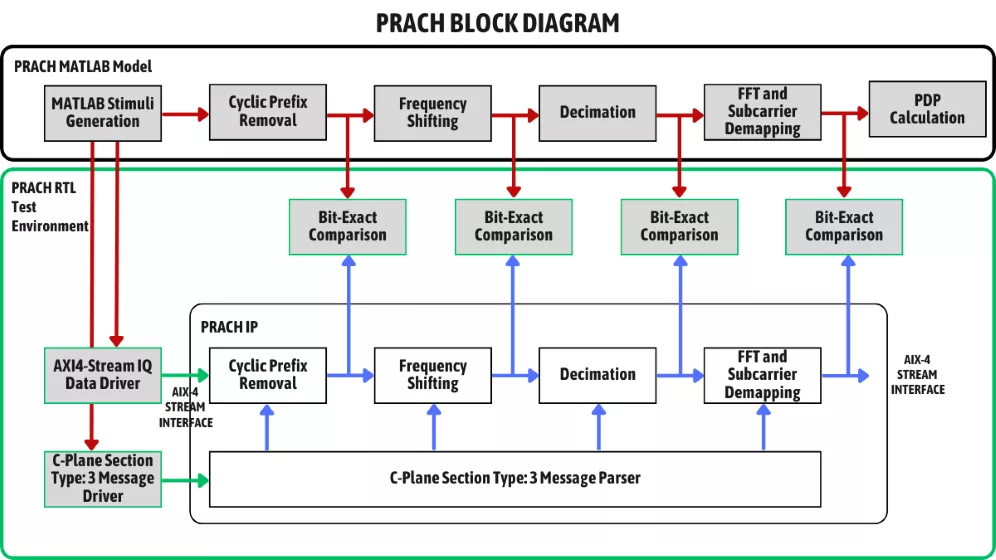

Optimize your 5G NR O-RAN Split 7.2X design with EIC cutting-edge PRACH Design and Verification Suite.

Note: some files may require an NDA depending on provider policy.

Optimize your 5G NR O-RAN Split 7.2X design with EIC cutting-edge PRACH Design and Verification Suite is a Cellular IP core from ElectraIC listed on Semi IP Hub.

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Cellular IP.

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.