3GPP 5G NR IP

Filter

Compare

20

IP

from

10

vendors

(1

-

10)

-

PUSCH Equalizer for 3GPP 5G NR

- Complete implementation of the relevant 3GPP standards

- Improved spectral efficiency across low SINR range against industry-standard simulation toolbox

-

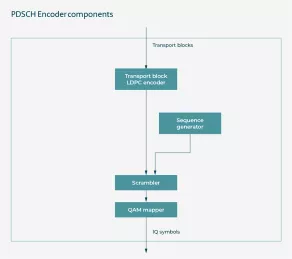

PDSCH Encoder for 3GPP 5G NR

- The PDSCH Encoder and PUSCH Decoder products simplify the creation of high performance 5G NR implementations.

- PDSCH Encoder features the new QAM mapper and Scrambler functionality. These are integrated with LDPC encoder chain and transport block chain components.

- PDSCH encoder has a configurable IQ parallelism for improved performance per clock.

- The functions included are CRC, Segmentation, LDPC encode, Rate matching, Integrated HARQ, Concatenation, Scrambling and Modulation.

-

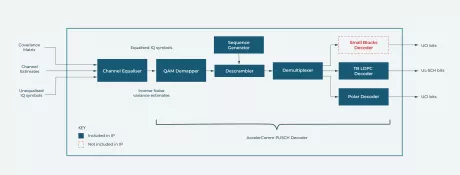

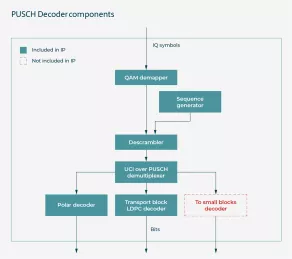

PUSCH Decoder for 3GPP 5G NR

- Complete implementation of the relevant 3GPP standard

- Improved BLER for UCI control data

-

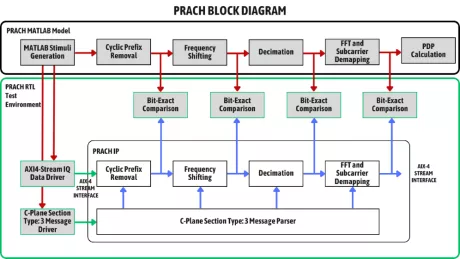

Optimize your 5G NR O-RAN Split 7.2X design with EIC cutting-edge PRACH Design and Verification Suite

- Comprehensive Support: All PRACH formats and configuration indexes described in 3GPP 38.211 are fully supported.

- Versatile Sequences: Length-139 and length-839 sequences are included.

- Frequency Multiplexing: Capable of decoding up to 8 frequencies multiplexed PRACHs.

-

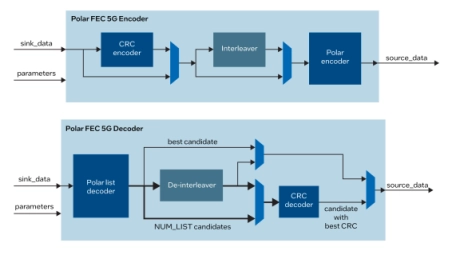

NR-5G Polar Decoder and Encoder

- The Forward Error Correction (FEC) sub-system is one of the essential basing blocks in any communication systems so a powerful FEC code is needed.

- The New Radio (NR) FEC for the control channel is proposed to be designed based on Polar codes allowing close to the Shannon limit/Capacity operation.

- The Polar code successive cancellation decoding process as needed for 3GPP physical layer standard.

-

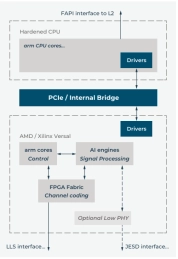

Modular, high performance 5G NR Layer 1 (PHY) solutions for Non-Terrestrial Network applications

- Complete implementation as per 3GPP standards and O-RAN SCF specifications.

- A full Layer 1 PHY designed and developed by AccelerComm™ using a mixture of hardware and software optimized to meet the needs of satellite vendors.

- Openly Licensable.

- Pre-integrated with AccelerComm™ LDPC and Polar encoder/decoder chains and inherits all the benefits from these highly performant products.

-

Polar Encoder / Decoder for 5G NR control channels

- The Polar core uses PC- and CRC-aided Successive Cancellation List decoding to achieve compromise-free error correction performance.

- Parallelism, latency, throughput and decoder list size are all configurable at synthesis time - including reducing list size below the standard list 8 - giving programme teams precise control over the power and performance trade-off for each target application.

-

5G Polar Intel® FPGA IP

- The 5G Polar Intel® FPGA IP implements a forward error correction (FEC) encoder and decoder based on polar codes compliant with the 3rd Generation Partnership Project (3GPP) 5G specification for integration into your wireless design

- Polar codes represent an emerging class of error correction supporting the high throughput requirements for 5G new radio (NR).

-

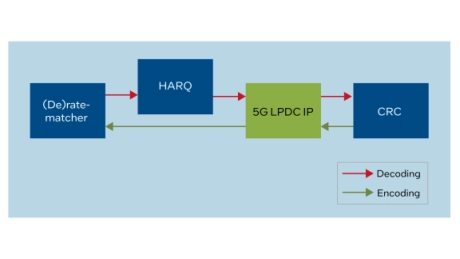

5G LDPC Intel® FPGA IP

- Low-density parity-check (LDPC) codes are linear error correcting codes that help you to transmit and receive messages over noisy channels

- The 5G LDPC and LDPC-V Intel® FPGA IP implement LDPC codes compliant with the 3rd Generation Partnership Project (3GPP) 5G specification for integration in your wireless design.

- LDPC codes offer better spectral efficiency than Turbo codes and support the high throughput for 5G new radio (NR).

-

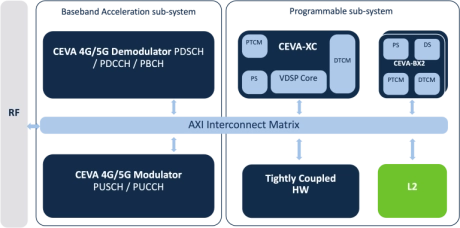

Scalable 5G modem platform

- The PentaG2 is a complete IP platform for implementing a wide range of user-equipment and IoT cellular modems.

- The platform includes a variety of DSPs, modem hardware modules, software libraries, and simulation tools.

- Capabilities of the PentaG2 include New Radio (NR) physical layer design ranging across all 3GPP profiles from RedCap IoT and mMTC, through eMBB up to ultra-reliable low-latency communications (URLLC).