28Gbps programmable SerDes PHY IP on UMC 28HPC IP

Filter

Compare

17

IP

from

2

vendors

(1

-

10)

-

12.5G Multiprotocol Serdes IP, Silicon Proven in UMC 28HPC

- A universal SERDES IP that operation from 1Gbps to 12.5 Gbps

- Compatible with PCIe/USB3/SATA base Specification

- Support 40-bit/32-bit/20-bit/16-bit parallel interface

- Support for PCIe2(5.0Gbps), USB3.0(5.0Gbps) and SATA3(6.0Gbps)

-

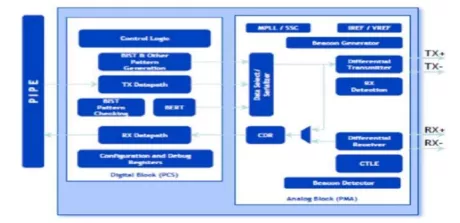

PCIe 2.0 Serdes PHY IP, Silicon Proven in UMC 40LP

- Compatible with PCIe base Specification

- Full compatible with PIPE3.0 interface specification

- Independent channel power down control

- Implemented Receiver equalization Adaptive-CTLE to compensate insertion loss

-

12.5G Multiprotocol Serdes IP, Silicon Proven in TSMC 28HPC+

- A universal SERDES IP that operation from 1Gbps to 12.5 Gbps

- Compatible with PCIe/USB3/SATA base Specification

- Support 40-bit/32-bit/20-bit/16-bit parallel interface

- Support for PCIe2(5.0Gbps), USB3.0(5.0Gbps) and SATA3(6.0Gbps)

-

PCIe 2.0 Serdes PHY IP, Silicon Proven in SMIC 14SF+

- Compatible with PCIe base Specification

- Full compatible with PIPE3.0 interface specification

- Independent channel power down control

- Implemented Receiver equalization Adaptive-CTLE to compensate insertion loss

-

PCIe 2.0 Serdes PHY IP, Silicon Proven in TSMC 40ULP

- Compatible with PCIe base Specification

- Full compatible with PIPE3.0 interface specification

- Independent channel power down control

- Implemented Receiver equalization Adaptive-CTLE to compensate insertion loss

-

PCIe 2.0 Serdes PHY IP, Silicon Proven in TSMC 16FFC

- Compatible with PCIe base Specification

- Full compatible with PIPE3.0 interface specification

- Independent channel power down control

- Implemented Receiver equalization Adaptive-CTLE to compensate insertion loss

-

PCIe 2.0 Serdes PHY IP, Silicon Proven in TSMC 12FFC

- Compatible with PCIe base Specification

- Full compatible with PIPE3.0 interface specification

- Independent channel power down control

- Implemented Receiver equalization Adaptive-CTLE to compensate insertion loss

-

PCIe 2.0 Serdes PHY IP, Silicon Proven in TSMC 7nm

- Compatible with PCIe base Specification

- Full compatible with PIPE4.2 interface specification

- Independent channel power down control

- Implemented Receiver equalization Adaptive-CTLE to compensate insertion loss

-

PCIe 3.0 Serdes PHY IP, Silicon Proven in GF 22FDX

- Silicon Proven in GF 22GDX with 0.8V and 1.8V power supply.

- Compatible with PCIe base Specification

- Support 32-bit/16-bit parallel interface

- Support for PCIe3(8.0Gbps)

-

PCIe 3.0 Serdes PHY IP, Silicon Proven in SMIC 12SF+/SF++

- Silicon Proven in SMIC 12SF+ with 0.8V and 1.8V power supply.

- Compatible with PCIe base Specification

- Support 32-bit/16-bit parallel interface

- Support for PCIe3(8.0Gbps)