100 Gbps Polar Decoder IP

Filter

Compare

58

IP

from

20

vendors

(1

-

10)

-

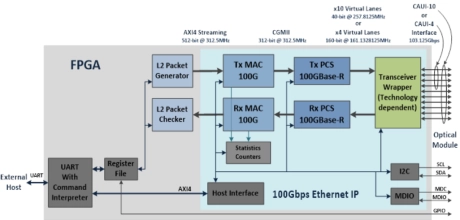

100 G Ethernet MAC & PCS IP Core

- The 100 Gbps Ethernet IP solution offers a fully integrated IEEE802.3ba compliant package for NIC (Network Interface Card) and Ethernet switching applications.

- Ethernet IP solution implements two user (application) side interfaces. The register configuration and control port is a 32-bit AXI4-Lite interface.

-

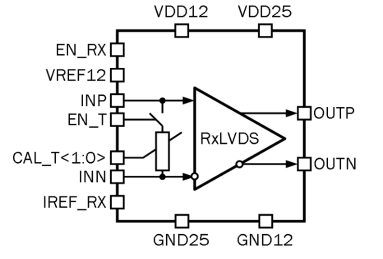

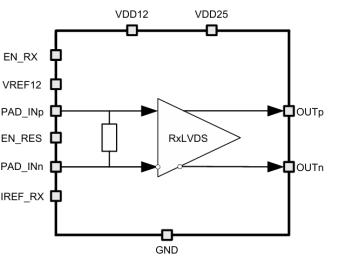

2 Gbps Rail to Rail LVDS receiver

- TSMC CMOS 65 nm

- 1.2 V CMOS input and output logic signals

- 2 Gbps (DDR MODE) switching rates

-

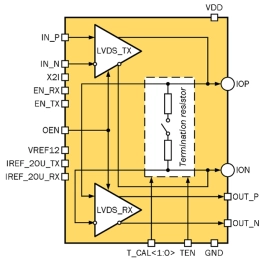

1.2 Gbps LVDS transmitter/receiver

- TSMC CMOS 180 nm

- 3.3 V power supply

- 1.2 Gbps (DDR MODE) switching rates (600 MHz)

- Half-duplex or full-duplex operation mode

-

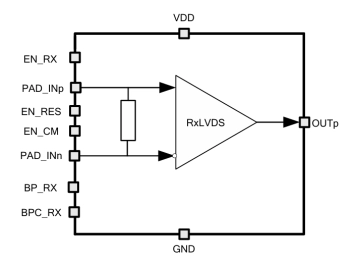

Rail to rail LVDS receiver 1 Gbps

- iHP SiGe BiCMOS 0.13 um

- 3.3 V power supply

- 1 Gbps (DDR MODE) switching rates

- Conforms to TIA/EIA-644 LVDS standards without hysteresis

-

1 Gbps DDR rail to rail LVDS receiver

- TSMC CMOS 0.065 um.

- 2.5 V analog power supply.

- 1.2 V digital power supply.

-

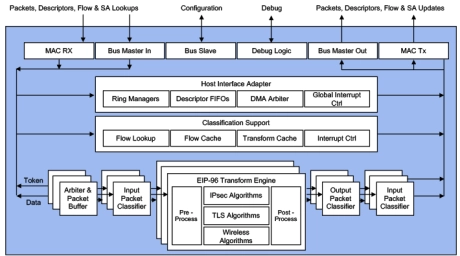

Multi-Protocol Engine with Classifier, Inline and Look-Aside, 10-100 Gbps

- Protocol aware IPsec, SSL, TLS, DTLS, 3GPP, MACsec packet engine with classifier and in-line interface for multi-core server processors

- 10-100 Gbps, programmable, maximum CPU offload by classifier, supports new and legacy crypto algorithms, streaming and AMBA interface

- Supported by Driver development kit, QuickSec IPsec toolkit, Linaro ODP.

-

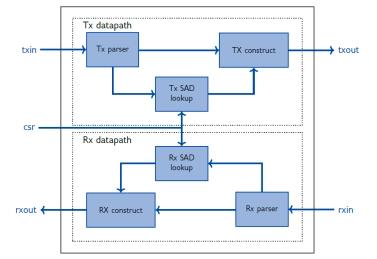

IPSEC AES-256-GCM (Standalone IPsec)

- XIP7213E implements the Internet Protocol Security (IPsec) as standardised in RFC4303 and RFC4305.

- The IPsec protocol defines a security infrastrucure for Layer 3 (as per the OSI model) traffic by assuring that a received packet has been sent by the transmitting station that claimed to send it.

-

Intel® Stratix® 10 FPGA H-Tile Hard IP for Ethernet Intel® FPGA IP Core

- Intel® Stratix® 10 FPGA H-Tile FPGA production devices include a configurable, hardened protocol stack for Ethernet that is compatible with the IEEE 802.3 High Speed Ethernet Standard.

-

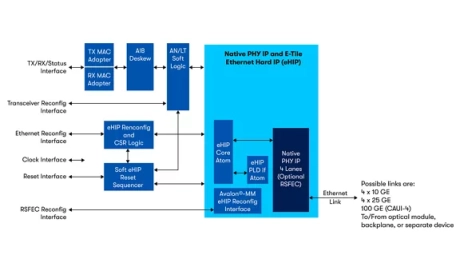

Intel® Agilex™ 7 and Intel® Stratix® 10 FPGA E-Tile Hard IP

- The Intel® Agilex™ 7 and Intel® Stratix® 10 FPGA E-Tile incorporates a configurable, hardened Ethernet protocol stack compatible with the IEEE 802.3 High-Speed Ethernet Standard and the 25G and 50G Ethernet Specification, Draft 1.6 from the 25G Ethernet Consortium

- The Intellectual Property (IP) core provides access to this hard IP at data rates of 10 Gbps, 25 Gbps, and 100 Gbps.

-

High-Speed Reed Solomon Intel® FPGA IP Core

- The High-Speed Reed Solomon Intel® FPGA intellectual property (IP) core uses a large parallel architecture to achieve a large throughput for applications that require 100 Gbps

- The IP core is suitable for 10G (such as OTN) or 100G Ethernet (IEEE 802.3bj/bm) applications.