SONET/SDH IP

Welcome to the ultimate SONET/SDH IP hub! Explore our vast directory of SONET/SDH IP

All offers in

SONET/SDH IP

Filter

Compare

12

SONET/SDH IP

from

5

vendors

(1

-

10)

-

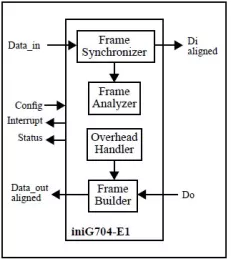

Universal G704-E1 Framer / Deframer Core

- The iniG704-E1 framer core is designed to handle synchronous frame structures (Recommondation G.704) running on E1 carrier.

- Transmit and receive part are designed as individual blocks, both independently handle basic and multi frames.

-

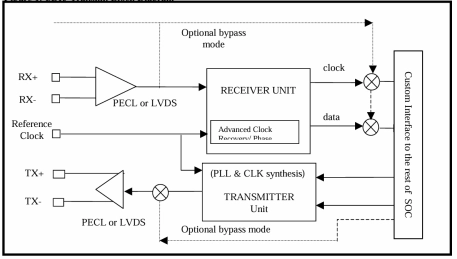

SONET/SDH OC-3 Transceiver/CDR

- The SMS2011 SONET/SDH is a fully integrated Clock Data Recovery (CDR) SONET OC-3 interface core designed for multiple integration on a single IC in a typical System-On-Chip (SOC) application.

- SMS2011 interfacing to the rest of building blocks on chip is fully customizable. For example, an optional mux demux module can be interconnected to the SMS2011 core making it capable of performing all the necessary serial-to-parallel and parallel to-serial functions in compliance with SONET/SDH transmission standards.

-

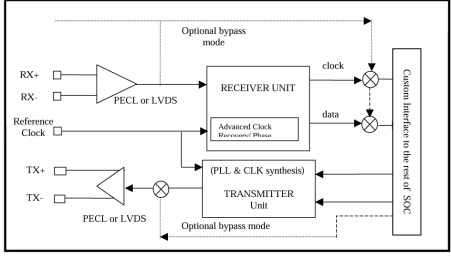

SONET/SDH OC-12 Transceiver/CDR

- The SMS2012 SONET/SDH is a fully integrated Clock Data Recovery (CDR) SONET OC-3 interface core designed for multiple integration on a single IC in a typical System-On-Chip (SOC) application.

- SMS2012 interfacing to the rest of building blocks on chip is fully customizable. For example, an optional mux demux module can be interconnected to the SMS2012 core making it capable of performing all the necessary serial-to-parallel and parallel to-serial functions in compliance with SONET/SDH transmission standards.

-

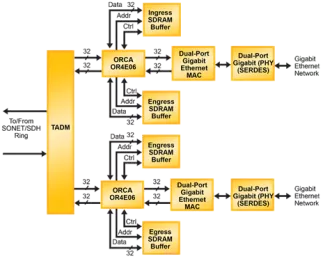

Quad GbE Over SONET/SDH

- Encapsulates GbE frames into SONET/SDH protocol using packet-over SONET (POS) and simplified data link (SDL)

- Quad OC-12c POS interface to the SONET/SDH network, each OC-12c carries one GbE data channel

- Performs all SONET/SDH section, line, and path termination functions

- Support for Jumbo Ethernet packets, up to 9.6 Kbytes

-

PoS Framer

- Best-in-Class size and performance.

- Multiple FPGA vendor support.

- Available for the following SONET/SDH rates:

- OC1/STM0, OC3/STM1, OC12/STM4, OC48/STM16, OC192/STM64

-

Fractional N PLL 8.5-11.3GHz in GF N65

- Clock monitor output

- Stand-by mode

- 1.2V Power Supply

- Adjustable (+/-30%) reference current

-

2G5 GFP-F (Framer)

- Compliant with ITU-T G.7041 specification.

- Best-in-Class size and performance with multiple FPGA vendor support.

- Interfaces to 2.6/2.5 gigabit data sources, such as Aliathon’s OTU1 and STM16 framer cores. Combines with Aliathon’s GFP-T Block Encoder core for GFP-T solutions, or may be used stand-alone for GFP-F solutions.

- Generates/Synchronises to a 16-bit wide GFP data stream including IDLE frames.

-

2G5 GFP-T (CODEC)

- Compliant with ITU-T G.7041 specification.

- Best-in-Class size and performance. Multiple FPGA vendor support.

- Accepts 64 byte blocks of data from an 8B/10B data source.

- Encodes input blocks into 67 byte GFP-T blocks as per G.7041.

-

SONET/SDH Framer

- Conforms to G.707, G.806, G.783 and T1.105

- Interfaces to the following SONET/SDH links:

- Performs frame generation, delineation and scrambling for one or multiple links.

- Detects Loss of Signal (LOS), Out of Frame (OOF) and Loss of Frame (LOF) defects.

-

SONET/SDH VT/TU Mapper

- Conforms to ITU G.707/ANSI T1.105.

- Maps/Demaps multiple Lower Order VT/TU paths:

- Inserts/Extracts PDH signals for VT/TU and STS/VC containers:

- Generates/Processes all VT/TU pointers. Calculates and inserts TX VT/TU BIP values. Provides a Path Overhead Insert/drop interface.