General Purpose PLL IP for UMC

Welcome to the ultimate

General Purpose PLL IP

for

UMC

hub! Explore our vast directory of

General Purpose PLL IP

for

UMC

All offers in

General Purpose PLL IP

for

UMC

Filter

Compare

182

General Purpose PLL IP

for

UMC

from

11

vendors

(1

-

10)

-

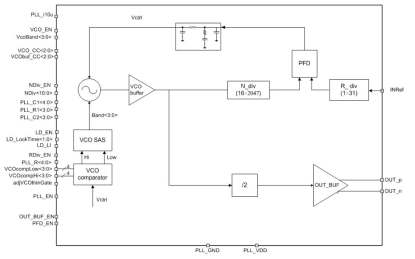

Phase-locked loop frequency synthesizer

- CMOS UMC 65 nm

- Integer-N frequency synthesizer with good phase noise performance

- Guaranteed frequency range 550…750 MHz

- Wide continuous loop frequency divider ratio range (16..2047 with step 1) allow to cover frequency range using different reference frequency

-

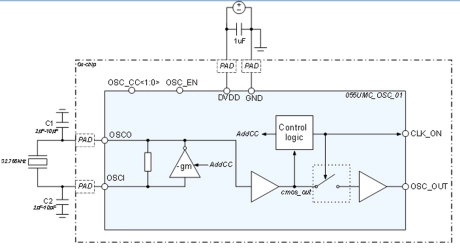

Ultra low power 32.768 kHz crystal oscillator

- UMC 55nm eFlash CMOS technology

- Input Voltage 1.2V

- Fixed 32.768kHz output frequency

-

Integer-N PLL, 32M ~ 256MHz on UMC 55nm

- This present IP is a Phase Locked Loop (PLL) circuit

- It’s analog PLL suitable for various frequency node generations

- The VCO can run from 32MHz to 256MHz

- It contains input clock divider (DIVM), a feedback clock divider (DIVN) and level shifter block to switch signals between VDD12 and VDD33

-

24-Bit Accuracy Fractional PLL; Support 8K~192K*256 Clock Output - UMC 55nm

- 24-Bit Accuracy Fractional PLL; Support 8K~192K*256 Clock Output

-

Wide Range Programmable Integer PLL on UMC L130EHS

- Electrically Programmable PLL for multiple applications

- Wide Ranges of Input and Output Frequency for diverse clocking needs

- Implemented with Analog Bits’ proprietary architecture using core logic devices only

- Fully integrated inside industry standard’s IO ring with proprietary low noise ESD structure

-

Aeonic Generate Clock Generation Module [PLL], 8x smaller than fractional analog solutions

- Process portable

- Proven (65nm to 3nm)

- Full SCAN testable

- Core voltage supply

-

UMC L65SP 65nm Ultra PLL - 15MHz-3000MHz

- New state-of-the-art architecture using high-speed digital and analog circuits that offers unprecedented operating ranges and extremely high performance.

- Ultra low jitter performance for the most demanding SerDes and ADC reference clocks.

- Ultra wide frequency range with multiplication factors over 250,000 to support 32KHz to 1GHz references.

- Precise frequency control with a least 26 fractional bits (at least 10 precise) for extremely high fractional-N resolution.

-

UMC L65SP 65nm General Purpose PLL - 260MHz-1300MHz

- Designed as a wide range clock multiplier with deskew capability.

- Delivers optimal jitter performance over all multiplication settings.

- Low area and low power.

- Suitable for system clock, DDR and general purpose applications.

-

UMC L65LP 65nm Ultra PLL - 15MHz-3000MHz

- New state-of-the-art architecture using high-speed digital and analog circuits that offers unprecedented operating ranges and extremely high performance.

- Ultra low jitter performance for the most demanding SerDes and ADC reference clocks.

- Ultra wide frequency range with multiplication factors over 250,000 to support 32KHz to 1GHz references.

- Precise frequency control with a least 26 fractional bits (at least 10 precise) for extremely high fractional-N resolution.

-

UMC L65LP 65nm General Purpose PLL - 120MHz-600MHz

- Designed as a wide range clock multiplier with deskew capability.

- Delivers optimal jitter performance over all multiplication settings.

- Low area and low power.

- Suitable for system clock, DDR and general purpose applications.