Memory Controller/PHY IP for TSMC

Welcome to the ultimate

Memory Controller/PHY IP

for

TSMC

hub! Explore our vast directory of

Memory Controller/PHY IP

for

TSMC

All offers in

Memory Controller/PHY IP

for

TSMC

Filter

Compare

32

Memory Controller/PHY IP

for

TSMC

from

4

vendors

(1

-

10)

Filter:

- 6nm

-

LPDDR6/5X/5 PHY V2 - TSMC N6

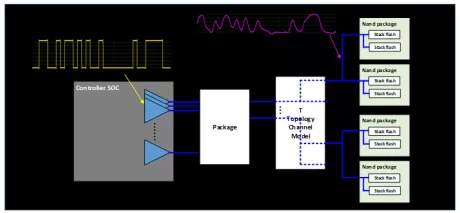

- The LPDDR6/5X/5 PHY IP enables ASICs, ASSPs, system-on-chips (SoCs), and system-in-package applications requiring high-performance LPDDR6, LPDDR5X, and/or LPDDR5 SDRAM interfaces operating at up to 14.4 Gbps

- With flexible configuration options, the LPDDR6/5X/5 PHY IP can be used in a variety of applications supporting LPDDR6, LPDDR5X, and/or LPDDR5 SDRAMs, precisely targeting the specific power, performance, and area (PPA) requirements of these systems

- LPDDR6 SDRAM’s combination of high bandwidth, capacity, low power, and cost effectiveness makes LPDDR6/5X/5 SDRAMs an attractive solution for traditional and new markets

- The LPDDR6/5X/5 PHY IP is designed to appeal to a variety of applications including: * Traditional mobile environments * Consumer products * Automotive solutions * Artificial intelligence * Data center applications

-

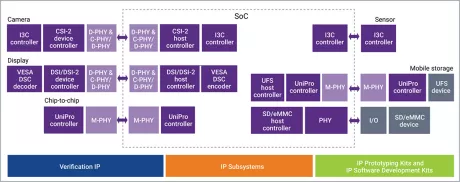

SD/eMMC - TSMC 6FF, North/South Poly Orientation

- Compliant with eMMC 5.1 HS400, SD 6.0 SDR104, DDR50, JESD8-7a (1.2V/1.8V) and JESD8c.01 (3.3V)

- Fully integrated hard macro with high speed IOs and DLL/delay lines

- Fine resolution DLL/delay lines for HS400 strobe and HS200/SDR104 auto-tuning

- Easy to integrate with the highly optimized Synopsys SD/eMMC Host Controller IP, providing a complete low risk solution

-

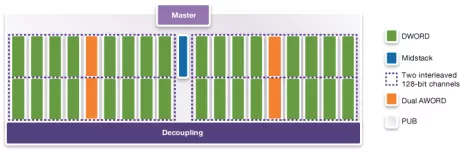

HBM2E PHY V2 - TSMC 6FF18

- Complete HBM2/HBM2E IP solution, including PHY, controller and verification IP, reduces integration risk while minimizing time-to-market

- 2.5D interposer expertise and reference designs

- Supports 2.5D-based JEDEC standard HBM2/HBM2E SDRAMs with data rates up to 3200 Mbps

-

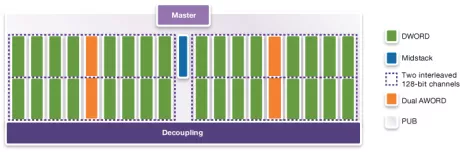

HBM2E PHY V2 (Hard 1) - TSMC 6FF18

- Complete HBM2/HBM2E IP solution, including PHY, controller and verification IP, reduces integration risk while minimizing time-to-market

- 2.5D interposer expertise and reference designs

- Supports 2.5D-based JEDEC standard HBM2/HBM2E SDRAMs with data rates up to 3200 Mbps

-

HBM3 PHY - TSMC N6

- Supports 2.5D-based JEDEC standard HBM3 DRAMs with data rates up to 9600 Mbps

- 16 independent 64-bit memory channels

- Pseudo-channel operation supported to enable up to 32 32-bit pseudo-channels with 1024-bit PHY

- Supports up to 4 trained frequencies with <5us switching time

-

HBM3 PHY (Hard 1) - TSMC N6

- Supports 2.5D-based JEDEC standard HBM3 DRAMs with data rates up to 9600 Mbps

- 16 independent 64-bit memory channels

- Pseudo-channel operation supported to enable up to 32 32-bit pseudo-channels with 1024-bit PHY

- Supports up to 4 trained frequencies with <5us switching time

-

LPDDR4X multiPHY - TSMC N6

- Supports JEDEC standard LPDDR4X, LPDDR4, LPDDR3, DDR4, DDR3, and DDR3L (1.35V DDR3) SDRAMs

- Support for data rates up to 4,267 Mbps (process dependent)

- Designed for rapid integration with Synopsys Enhanced Universal DDR Memory/Protocol Controllers (uMCTL2/uPCTL2) for a complete DDR interface solution

- PHY independent, firmware-based training using an embedded calibration processor

-

LPDDR5/4/4X PHY - TSMC N6

- Supports JEDEC standard LPDDR5X, LPDDR5, LPDDR4 and LPDDR4X SDRAMs

- Support for data rates up to 6400 Mbps

- Designed for rapid integration with Synopsys’ LPDDR5/4/4X controller for a complete DDR interface solution

- DFI 5.0 controller interface

-

DDR5/4 PHY V2 - TSMC N6

- Supports JEDEC standard DDR5 and DDR4 SDRAMs

- High-performance DDR PHY supporting data rates up to 8400 Mbps

- PHY independent, firmware-based training using an embedded calibration processor

- Supports up to 4 trained states/ frequencies with <3μs switching time

-

ONFI IO v5.1, 3.6GT/s, TSMC N6, 1.2V, N/S orientation, H&V cell

- Supports ONFI 6.0(4.8Gbps), ONFI 5.1(3.6Gbps), ONFI 5.0(2.4Gbps), ONFI 4.1(1.2Gbps), ONFI 4.0(800Mbps) & ONFI 3.2(533Mbps)

- Power-sequence free

- Provides multi-driving-strength selection

- Provides CTT mode and LTT mode