Building Blocks IP for TSMC

Welcome to the ultimate

Building Blocks IP

for

TSMC

hub! Explore our vast directory of

Building Blocks IP

for

TSMC

All offers in

Building Blocks IP

for

TSMC

Filter

Compare

7

Building Blocks IP

for

TSMC

from

6

vendors

(1

-

7)

-

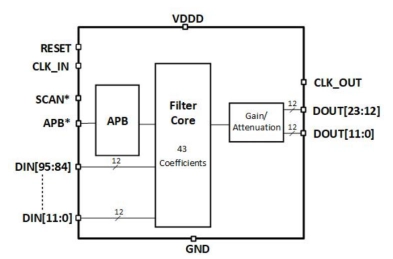

12-bit 250MHz Decimation filter with 43 taps

- Programmable Coefficients

- Programmable gain/attenuation at the output

- 4X Decimation Factor

-

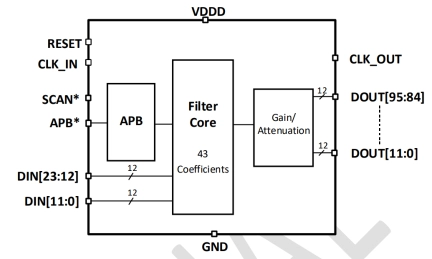

12-bit 250MHz interpolation filter with 43 taps on TSMC 16nm

- The ODT-DSP-INT-43T250M-T16 is a 12-bit 250MHz interpolation filter with 43 taps in a 12/16nm CMOS process.

- The 43 Tap interpolation filter increases output data rate (fDOUT) to the DAC by four relative to its original input data rate(fDIN).

-

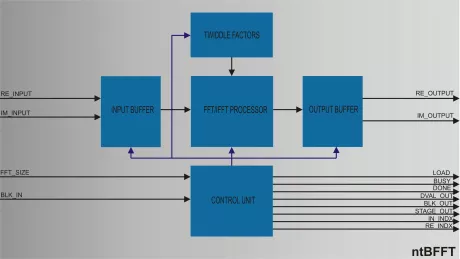

Fully Configurable Radix 2 FFT/IFFT Processor

- Radix-2 Fast Fourier Transform processor IP Core.

- Same IP core may be used to compute both FFT and IFFT transforms without any complexity overhead.

- Highly parameterizable/scalable design using generic I/O fixed point precision and generic internal calculations precision.

- Bit true Matlab script model is provided to aid core fixed point precision configuration for any target application.

-

Configurable SPDIF-AES3 Receiver

- The SPDIF-Rx-Pro (CWda14) is a digital audio receiver IP core supporting the SPDIF and AES3 and IEC60958 standards and also adds hardware support for the IEC61937 and SMPTE 337M standards for non-PCM (compressed) audio.

- This purely digital clock and data recovery method dispenses the classical analog PLL at the input reducing the receiver cost.

-

Fast Fourier Transformation

- The FFT is a fully customizable FFT. The key features are free choose of the FFT dimension, data width and an additional output with the absolute value of the spectrum.

-

Multi-Channel Signature Calculator

- Works on several data blocks in parallel

- Configurability: packet size, number of windows, internal memory parameters

- AXI interfaces for data and control

- DMA results write-out