Chiplet and D2D IP for TSMC

Welcome to the ultimate

Chiplet and D2D IP

for

TSMC

hub! Explore our vast directory of

Chiplet and D2D IP

for

TSMC

All offers in

Chiplet and D2D IP

for

TSMC

Filter

Compare

42

Chiplet and D2D IP

for

TSMC

from

6

vendors

(1

-

10)

-

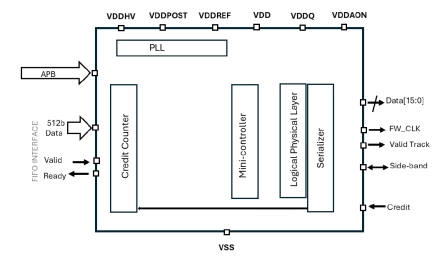

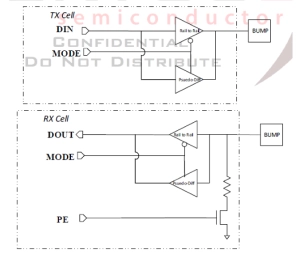

UCIe TX Interface

- Transmit-only UCIe REV1.1 with FIFO Interface

- TSMC 16FFC process

- Low power UCIe D2D

- 1 pJ/bit at 0.7V

-

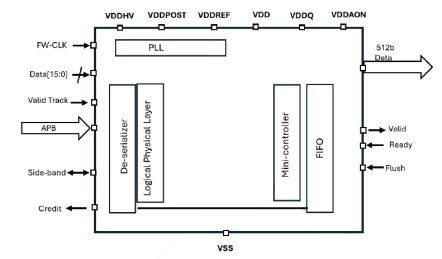

UCIe RX Interface

- Receive-only UCIe Rev1.1 with FIFO Interface

- Samsung 8nm process

- Low power UCIe D2D

- 1 pJ/bit at 0.7V

-

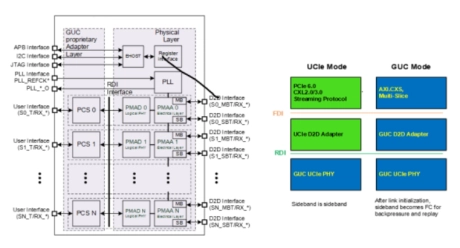

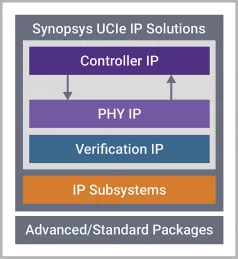

TSMC CLN5FF GUCIe LP Die-to-Die PHY

- IGAD2DY11A is an LP (Low Power) Die-to-Die (D2D) PHY for SoIC-X Face-to-Face advanced package.

- This GUCIe PHY not only supports UCIe specification rev 1.1 compliance physical layer and Raw D2D interface (RDI) but also optionally provides the

-

<4Gbps Low Power D2D Interface in TSMC 16nm & 28nm

- A <4Gbps, Wide I/O Compatible, Die to Die Interface in TSMC 16nm and 28nm.

- This silicon proven die to die interface includes IP in both TSMC 16nm FFC/FFC+ and 28nm HPM/HPC/HPC+.

- The I/O cells for both versions of the library are defined as TX only and RX only.

-

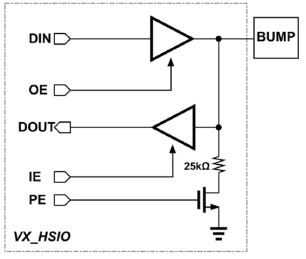

Low Power D2D Interface in TSMC 16nm FFC/FFC+

- This library is a production-quality, silicon-proven custom Die-to-Die high speed interface available in TSMC’s 16nm process.

- The I/O cell is bidirectional, has two modes of operation: standard full rail to rail swing, or a custom low noise pseudo-differential interface.

- The RX cells have a weak pull-down feature.

-

Die-to-Die, High Bandwidth Interconnect PHY Ported to TSMC N7 X24

- Delivers up to 4Gbps per pin with up to bidirectional 2 Tbps/mm of die edge

- High-bandwidth, low-power, low-latency multi-channel PHY in applications requiring connections between dies within a package

- Compliant with Intel Advanced Interface Bus (AIB) v1.1 standard

- Compliant with IEEE 1149.1 (JTAG), 1149.6 (AC JTAG) for easy integration with SoC testability framework

-

Die-to-Die, High Bandwidth Interconnect PHY Ported to TSMC N5 X24, North/South (vertical) poly orientation

- Delivers up to 4Gbps per pin with up to bidirectional 2 Tbps/mm of die edge

- High-bandwidth, low-power, low-latency multi-channel PHY in applications requiring connections between dies within a package

- Compliant with Intel Advanced Interface Bus (AIB) v1.1 standard

- Compliant with IEEE 1149.1 (JTAG), 1149.6 (AC JTAG) for easy integration with SoC testability framework

-

Die-to-Die, 112G Ultra-Extra Short Reach PHY Ported to TSMC N7 X16, North/South (vertical) poly orientation

- 16-lane TX and RX square macros for placement in any edge of the die

- Supports 2.5G to 112G data rates, enabling very high bandwidth per mm of beachfront for die-to-die and die-to-optical engine connectivity

- Implements NRZ and PAM-4 signaling

- Meets the performance, efficiency, and reliability requirements of die-to-die interconnects

-

Die-to-Die, 112G Ultra-Extra Short Reach PHY Ported to TSMC N6 X16, North/South (vertical) poly orientation

- 16-lane TX and RX square macros for placement in any edge of the die

- Supports 2.5G to 112G data rates, enabling very high bandwidth per mm of beachfront for die-to-die and die-to-optical engine connectivity

- Implements NRZ and PAM-4 signaling

- Meets the performance, efficiency, and reliability requirements of die-to-die interconnects

-

Die-to-Die, 112G Ultra-Extra Short Reach PHY Ported to TSMC N5 X16, North/South (vertical) poly orientation

- 16-lane TX and RX square macros for placement in any edge of the die

- Supports 2.5G to 112G data rates, enabling very high bandwidth per mm of beachfront for die-to-die and die-to-optical engine connectivity

- Implements NRZ and PAM-4 signaling

- Meets the performance, efficiency, and reliability requirements of die-to-die interconnects