General Purpose PLL IP for TSMC

Welcome to the ultimate

General Purpose PLL IP

for

TSMC

hub! Explore our vast directory of

General Purpose PLL IP

for

TSMC

All offers in

General Purpose PLL IP

for

TSMC

Filter

Compare

203

General Purpose PLL IP

for

TSMC

from

18

vendors

(1

-

10)

-

1.7GHz Multiplying PLL on TSMC 28nm

- Including Loop-filter

- VCO operating range : 850MHz - 1700 MHz

- Output frequency range : 850MHz -1700 MHz

- Input frequency range : 9.6MHz - 216MHz

-

5GHz Multiplying PLL on TSMC 28nm

- Including Loop-filter

- VCO operating range : 2500MHz - 5000 MHz

- Output frequency range : 1250MHz - 2500 MHz

- Input frequency range : 12MHz - 320 MHz

-

1.8GHz SSCG PLL on TSMC 28nm HPC+

- Including Loop-filter

- VCO operating range : 900MHz - 1800 MHz

- Output frequency range : 900MHz-1800 MHz

- Input frequency range : 12MHz - 192MHz

-

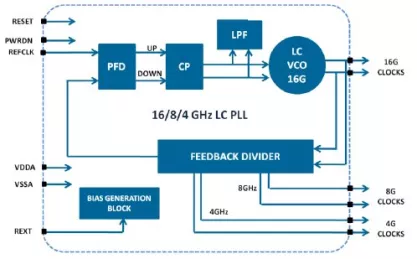

High Speed 16GHz PLL

- Type II ,3rd order low jitter PLL

- Auto calibration for process and temperature (USP)

- Programmable frequency using CSR registers

- 8/10/16GHz quadrature clocks

- Operating temperature -40 to 125

-

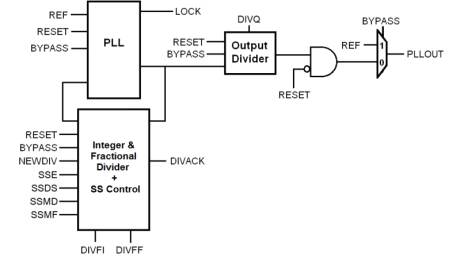

Core Powered Wide Range Programmable Integer PLL on TSMC CLN2P

- Electrically Programmable PLL with Fractional-N divide and Spread Spectrum Clock Generation

- Entirely core voltage powered, needs no analog supply voltage

- Wide Ranges of Input and Output Frequency for diverse clocking needs

- Very fine precision: near 1 part per billion resolution

-

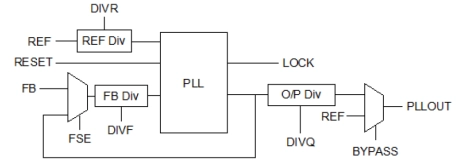

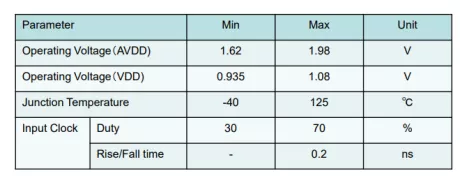

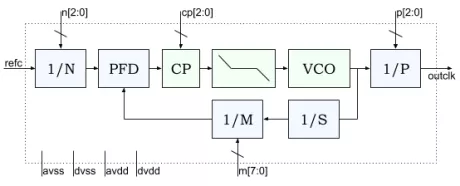

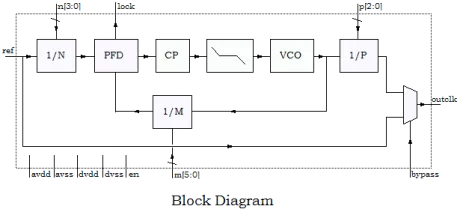

Low Power PLL for TSMC 40nm ULP

- Wide range M, P, and N integer dividers.

- 40MHz – 600MHz output frequency range.

- Input frequency range 1.4MHz – 32MHz.

- 18pS RMS cycle to cycle jitter.

- Lock-detect function.

- Optional bypass function.

-

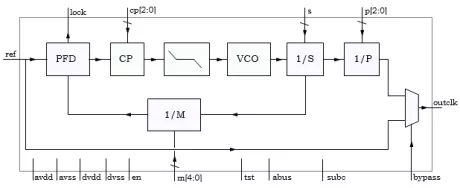

General Purpose PLL for TSMC 152nm

- Wide range M integer divider. (See ot3122 for M, N, and P dividers)

- 40MHz – 800MHz output frequency range.

- Comparable frequency range 8MHz – 32MHz.

- Optional prescaler.

- 19pS RMS cycle to cycle jitter at 800MHz.

- Lock-detect function.

- Bypass function.

- 20µS well defined fast startup behavior.

-

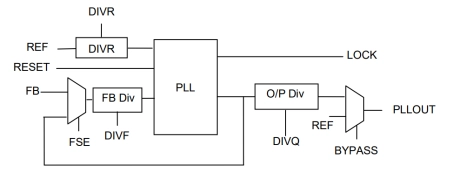

PLL for TSMC 130nm LP

- Wide range N, M, P integer dividers.

- 40MHz – 600MHz output frequency range.

- Comparable frequency range 8MHz – 50MHz.

- 18pS RMS cycle to cycle jitter at 400MHz.

- Lock-detect function.

- Bypass function.

- Well defined startup behavior.

- -40°C to 125°C temperature operation.

- Small cell area: 0.022mm2 in 0.13µ CMOS.

-

Wide Range Programmable Integer PLL on TSMC CLN80GC

- Electrically Programmable PLL for multiple applications

- Wide Ranges of Input and Output Frequency for diverse clocking needs

- Implemented with Analog Bits’ proprietary architecture

- Fully integrated inside customer-specified IO ring

-

Wide Range Programmable Integer PLL on TSMC CLN5A

- Electrically Programmable PLL for multiple applications

- Wide Ranges of Input and Output Frequency for diverse clocking needs

- Implemented with Analog Bits’ proprietary architecture

- Small area footprint