Clock Synthesizer IP for TSMC

Welcome to the ultimate

Clock Synthesizer IP

for

TSMC

hub! Explore our vast directory of

Clock Synthesizer IP

for

TSMC

All offers in

Clock Synthesizer IP

for

TSMC

Filter

Compare

11

Clock Synthesizer IP

for

TSMC

from

5

vendors

(1

-

10)

-

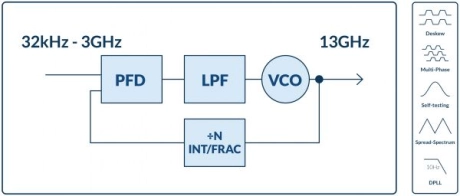

General-purpose & Specialized Ring PLLs + RTL-based Solutions

- Wide functional range allows all frequencies in a system to be synthesized with one PLL macro

- Input & output frequency ranges greater than 1000:1

-

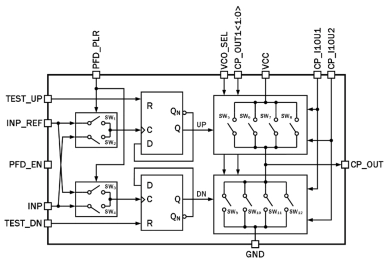

0.1 to 25 MHz Phase-frequency detector with charge pump

- TSMC BiCMOS SiGe 180 nm

- Input signals with low amplitude

- Low disbalance of output current

- Reference frequency from 0.1 MHz to 25 MHz

-

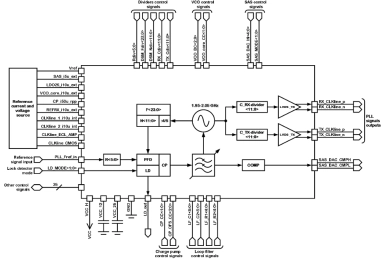

1 to 50 MHz phase-locked loop frequency synthesizer

- TSMC CMOS 55 nm

- Output frequency range from 1 MHz to 50 MHz

- Reference frequency range from 5 MHz to 50 MHz

-

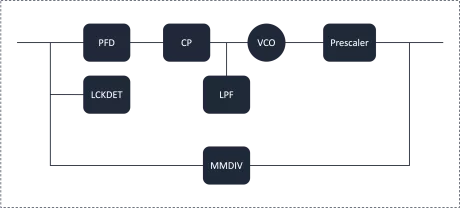

14GHz Integer-N High-Speed PLL

- Type II hybrid Integer-N LC-PLL

- Quadrature clocks at 14GHz and 7GHz

- Fast locking

-

Real-Time-Clock Analog, Include 32K XOSC, Capaless LDO, POR, VDT - TSMC 28nm

- Real-Time-Clock Analog, Include 32K XOSC, Capaless LDO, POR, VDT;

-

Real-Time-Clock Analog, Include 32K XOSC, Capaless LDO, POR, VDT - TSMC 28nm

- Real-Time-Clock Analog, Include 32K XOSC, Capaless LDO, POR, VDT;

-

Real-Time-Clock with Temperature Compensation - TSMC 40nm

- Real-Time-Clock with Temperature Compensation

-

Real-Time-Clock Analog, Include 32K XOSC, Capaless LDO, POR, VDT - TSMC 7nm

- Real-Time-Clock Analog, Include 32K XOSC, Capaless LDO, POR, VDT;

-

Real-Time-Clock Analog, Include 32K XOSC, Capaless LDO, POR, VDT - TSMC 28nm

- Real-Time-Clock Analog, Include 32K XOSC, Capaless LDO, POR, VDT;

-

Real-Time-Clock Analog, Include 32K XOSC, Capaless LDO, POR, VDT - TSMC 22nm

- Real-Time-Clock Analog, Include 32K XOSC, Capaless LDO, POR, VDT;