Clocking IP for TSMC

Welcome to the ultimate

Clocking IP

for

TSMC

hub! Explore our vast directory of

Clocking IP

for

TSMC

All offers in

Clocking IP

for

TSMC

Filter

Compare

1,293

Clocking IP

for

TSMC

from

30

vendors

(1

-

10)

-

1.7GHz Multiplying PLL on TSMC 28nm

- Including Loop-filter

- VCO operating range : 850MHz - 1700 MHz

- Output frequency range : 850MHz -1700 MHz

- Input frequency range : 9.6MHz - 216MHz

-

5GHz Multiplying PLL on TSMC 28nm

- Including Loop-filter

- VCO operating range : 2500MHz - 5000 MHz

- Output frequency range : 1250MHz - 2500 MHz

- Input frequency range : 12MHz - 320 MHz

-

1.8GHz SSCG PLL on TSMC 28nm HPC+

- Including Loop-filter

- VCO operating range : 900MHz - 1800 MHz

- Output frequency range : 900MHz-1800 MHz

- Input frequency range : 12MHz - 192MHz

-

3.2GHz SSCG PLL on TSMC 12nm

- Including Loop filter

- VCO operating range : 1600MHz- 3200MHz

- Output frequency range: 400MHz- 3200MHz

- Input frequency range : 10MHz- 200MHz

-

4.3GHz SSCG PLL on TSMC 7nm

- Including Loop filter

- VCO operating range : 2000MHz-4300MHz

- Output frequency range: 500MHz-4300MHz

- Input frequency range : 10MHz- 200MHz

-

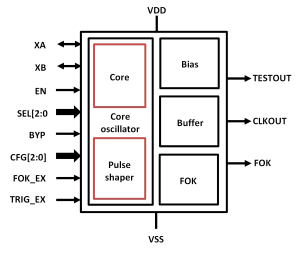

Ultra low-power crystal-based 32 kHz oscillator in TSMC 12FFC+

- OSC-XT-32k-T12FFC.01_TSMC_12_FFC+ is an ultra-low power crystal-based oscillator in TSMC 12FFC+ for accurate 32 kHz clock generation in the SoC Always-On domain (eg. implementation of RTC features).

- An embedded auxiliary loop controls the voltage amplitude at the crystal terminals for maximizing the power efficiency for multiple crystals.

-

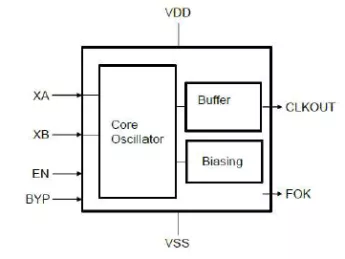

Ultra low-power crystal-based 32 kHz oscillator designed in TSMC 22ULL

- High accuracy

- Low power consumption

- Compatible with a large range of crystals

- Bypass mode for enabling fast testing capabilities

-

Low-power 32 kHz RC low-drift oscillator in TSMC 22ULL

- OSC-RC-32k-LD-A01-T22ULL.01_TSMC_22_ULL is a 32 kHz RC oscillator in TSMC 22ULL specifically designed for the implemenation of accurate time-based features in always-on domains.

- With an overall precision better than 500 ppm on its full voltage and temperature operating ranges, Dolphin's IP meets the sleep clock accuracy requirements of the BLE standard, removing the need for an external crystal.

-

Low-power 32 kHz RC oscillator in TSMC 22ULL 1.8 V

- OSC-RC-32k-A01-D18-T22ULL.03_TSMC_22_uLL1.8 is a 32 kHz RC oscillator in TSMC 22ULL with 1.8 V I/O MOSFET devices based on a low-power architecture for the implementation of always-on domains.

- The IP informs the host when the frequency has reached a stable frequency value after leaving shutdown or standby mode.

-

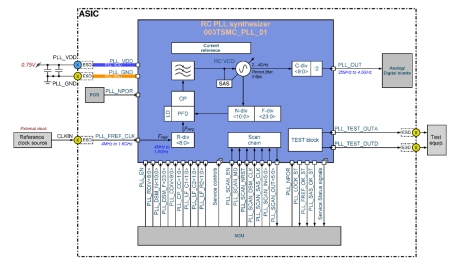

25MHz to 4.0GHz Fractional-N RC PLL Synthesizer on TSMC 3nm N3P

- Fractional-N Phase locked loop frequency synthesizer is intended for ASIC clock generation.

- The Fractional-N PLL loop with 2GHz-4GHz VCO has high phase noise performance and ultra-fine frequency tuning step.

- VCO Sub-band auto select (SAS) system allows to find automatically appropriate sub-band for VCO on locked PLL.