MIPI D-PHY IP for SMIC

Welcome to the ultimate

MIPI D-PHY IP

for

SMIC

hub! Explore our vast directory of

MIPI D-PHY IP

for

SMIC

All offers in

MIPI D-PHY IP

for

SMIC

Filter

Compare

19

MIPI D-PHY IP

for

SMIC

from

6

vendors

(1

-

10)

-

MIPI D-PHY IP

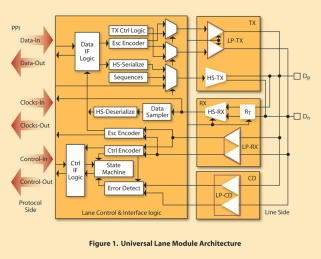

- The D-PHY is partitioned into a Digital Module – CIL (Control and Interface Logic) and a Mixed Signal Module. It is provided as a combination of Soft IP views (RTL, and STA Constraints) for Digital Module, and Hard IP views (GDSII/CDL/LEF/LIB) for the Mixed Signal Module.

- This unique offering of Soft and Hard IP permits architectural design flexibility and seamless implementation in customer-specific design flow.

-

MIPI DPHY v1.2 Tx 4 Lanes - SMIC 28PS 1.8V, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI DPHY v1.2 Rx 4 Lanes - SMIC 28PS 1.8V, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI DPHY Gen2 Bidirectional 4 Lanes - SMIC 28HKMG 1.8V, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI DPHY

- Silicon proven in 22, 28, 55, 110nm from Global Foundries, Samsung and SMIC

- Compliant to the MIPI D-PHY spec v1.1 (SEC28/SMIC55/SMIC110)

- Lane type:1 clock + 4 data, bi-directional

- Built-in self test function

-

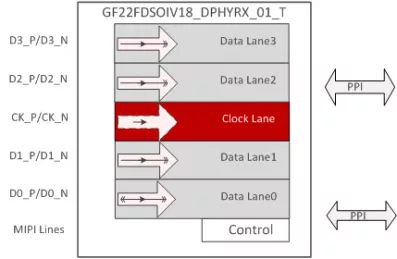

MIPI DPHY-RX

-

Data rate per lane: High-Speed mode 80M~2.5G bps, Low-Power mode 10Mbps

-

Silicon proven in GlobalFoundries 22FDX process

-

Compliant to the MIPI D-PHY spec v1.2

-

Lane type:1 clock + 4 data(D0 is bi-dir)

-

Support for DPHY Ultra Low Power State

-

-

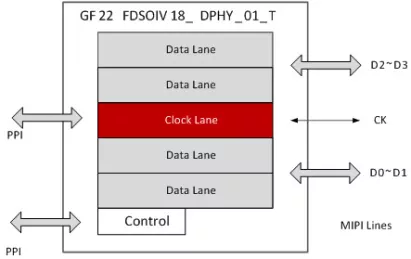

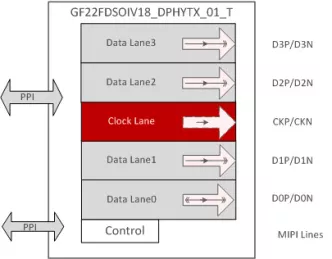

MIPI DPHY-TX - GlobalFoundries 22FDX process

- Data rate per lane: High-Speed mode 80M~2.5G bps, Low-Power mode 10Mbps

- Silicon proven in GlobalFoundries 22FDX process

- Compliant to the MIPI D-PHY spec v1.2

- Support HiSPi-SLVS TX compatible mode

-

GLOBALFOUNDRIES 22nm FDX MIPI DPHY Slave V1.2

- Process: GLOBALFOUNDARIES 22nm FDSOI 0.8V/1.8V

- 80 to 2500 Mbps data rate per lane in DPHY HS mode

- 80 to 2500 Msps symbol rate per lane in CPHY HS mode

- All lanes support HS and ULPS modes in forward direction

-

MIPI D-PHY Bidir 2/4L

- ? Attachable PLL clock multiplication unit for master-side functionality

- ? Flexible input clock reference — 5 MHz to 500 MHz

- ? 50% DDR output clock duty-cycle

- ? Lane operation ranging from 80 Mbps to 1.5 Gbps in forward direction

-

MIPI D-PHY RX/TX v1.1 / v1.2 IP in TSMC (12/16nm, 28nm, 40nm, and 55nm process)

- Compliant with MIPI D-PHY specification up to v1.2/v1.1 (by different process nodes)

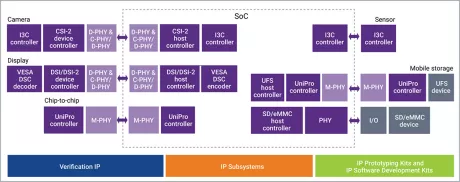

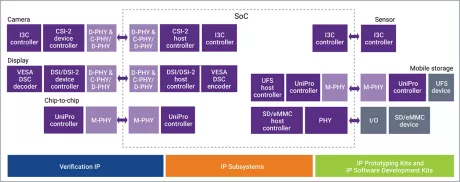

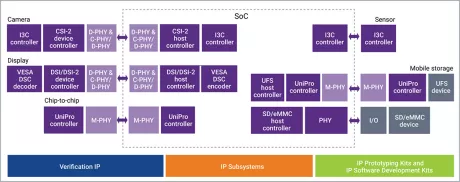

- Supports MIPI DSI and CSI-2 protocols

- Supports HS data rates up to 2.5Gbps (v1.2, per lane) . 1.5Gbps(v1.1, per lane)

- Supports LS data rate of 10Mbps and Ultra-low power modes