MIPI IP for SMIC

Welcome to the ultimate

MIPI IP

for

SMIC

hub! Explore our vast directory of

MIPI IP

for

SMIC

All offers in

MIPI IP

for

SMIC

Filter

Compare

23

MIPI IP

for

SMIC

from

7

vendors

(1

-

10)

-

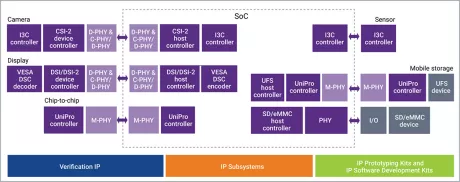

MIPI D-PHY IP

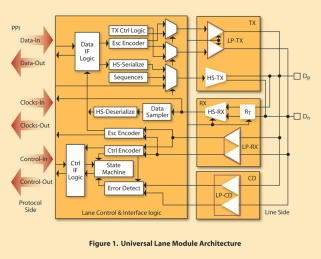

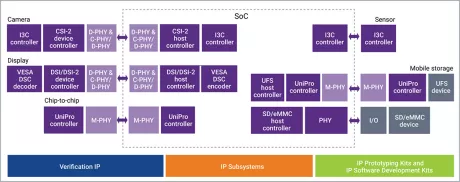

- The D-PHY is partitioned into a Digital Module – CIL (Control and Interface Logic) and a Mixed Signal Module. It is provided as a combination of Soft IP views (RTL, and STA Constraints) for Digital Module, and Hard IP views (GDSII/CDL/LEF/LIB) for the Mixed Signal Module.

- This unique offering of Soft and Hard IP permits architectural design flexibility and seamless implementation in customer-specific design flow.

-

MIPI M-PHY IP

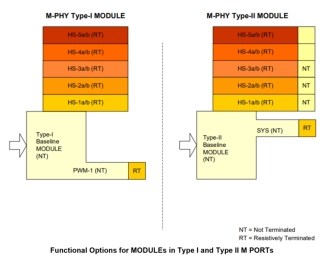

- The MIPI M-PHY is a high-frequency low-power, Physical Layer IP that supports the MIPI® Alliance Standard for M-PHY.

- The IP can be used as a physical layer for many applications, connecting flash memory-based storage, cameras and RF subsystems, and for providing chip-to-chip inter-processor communications (IPC).

-

MIPI DPHY v1.2 Tx 4 Lanes - SMIC 28PS 1.8V, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI DPHY v1.2 Rx 4 Lanes - SMIC 28PS 1.8V, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI DPHY Gen2 Bidirectional 4 Lanes - SMIC 28HKMG 1.8V, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI DPHY

- Silicon proven in 22, 28, 55, 110nm from Global Foundries, Samsung and SMIC

- Compliant to the MIPI D-PHY spec v1.1 (SEC28/SMIC55/SMIC110)

- Lane type:1 clock + 4 data, bi-directional

- Built-in self test function

-

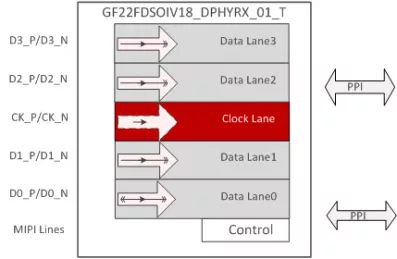

MIPI DPHY-RX

-

Data rate per lane: High-Speed mode 80M~2.5G bps, Low-Power mode 10Mbps

-

Silicon proven in GlobalFoundries 22FDX process

-

Compliant to the MIPI D-PHY spec v1.2

-

Lane type:1 clock + 4 data(D0 is bi-dir)

-

Support for DPHY Ultra Low Power State

-

-

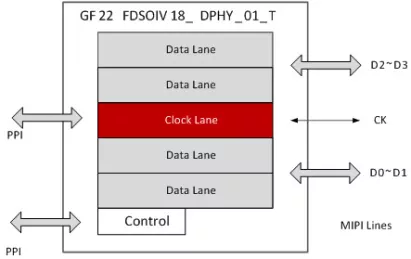

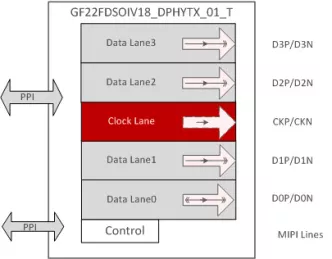

MIPI DPHY-TX - GlobalFoundries 22FDX process

- Data rate per lane: High-Speed mode 80M~2.5G bps, Low-Power mode 10Mbps

- Silicon proven in GlobalFoundries 22FDX process

- Compliant to the MIPI D-PHY spec v1.2

- Support HiSPi-SLVS TX compatible mode

-

MIPI RX controller on SMIC 28nm

- MIPI RX controller is a mass production IP in SMIC 28nm supported MIPI DSI & DCS protocols.

-

MIPI RX PHY on SMIC 28nm

- MIPI RX PHY is a mass production IP for D-PHY v1.2 and C-PHY v1.2 protocols

- It includes a total of 5 Lanes, among which there are 4 data lanes and 1 clock lane.