Regulator IP for SMIC

Welcome to the ultimate

Regulator IP

for

SMIC

hub! Explore our vast directory of

Regulator IP

for

SMIC

All offers in

Regulator IP

for

SMIC

Filter

Compare

26

Regulator IP

for

SMIC

from

3

vendors

(1

-

10)

-

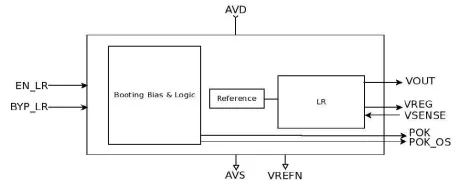

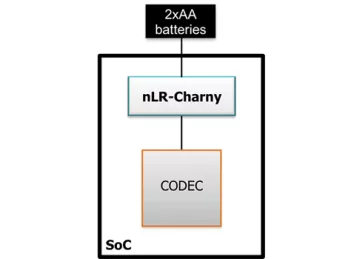

Linear regulator, low-noise optimized for sensitive analog loads such as CODEC and Reference

- Starring a PSRR of -65 dB at 20 kHz and a low intrinsic noise, combined with a low quiescent current of 110 uA, the nLR-VAIPO helps optimize the power management network for audio handheld applications such as smartphone and tablet.

- Small footprint: only 0.12 mm2 (including bandgap reference and POK circuit)

- Minimization of the overall system power, through the support of 3 modes of operation: normal, shutdown and bypass

- Eases integration in SoC nLR-VAIPO is delivered with behavioral models. These new views enable to build an optimized Power Management Network (PMNet) by verifying mode transitions as well as noise propagation.

-

Linear Regulator, Low Noise optimized for sensitive application such as RF or PLL blocks

- Low noise: high power Supply Rejection Ratio (PSRR): - 65 dB at F < 10 kHz

- Low intrinsic noise: 20 uVRMS at 10 Hz to 20 kHz

- Low Bill-of-Material: optimized in density for the best trade-off for the given output current and input voltage range

- Cost efficient solution compared to external Power Management.

-

LDO regulator on SMIC 40nm, 0.6~1.1v output

- The present IP is a low dropout voltage regulator, which can support 10uA current load

- The input voltage is 2.7-3.6V (typical: 3.3V)

- Its output voltage range is 0.6-0.8-1.1V

- The reference voltage and bias current are 0.6-0.8-1.1V and 0.5uA from BGR, respectively.

-

LDO regulator on SMIC 40nm, 2.1v output

- The present IP is a low dropout voltage regulator, which can support 360uA current load

- The input voltage is 2.7-3.6V (typical: 3.3V)

- Its output voltage is 2.1V

- The reference voltage and bias current are 1.2V and 0.5uA from BGR.

-

LDO regulator on SMIC 40nm, 1.13v output

- The present IP is a low dropout voltage regulator, which can support 10uA DC current load

- The input voltage is 2.7-3.6V (typical: 3.3V)

- Its output voltage range is 0.62V-1.13V-1.75V

- The reference voltage and bias current are 0.6V and 0.5uA from BGR, respectively.

-

LDO regulator on SMIC 40nm, 1.42v output

- The present IP is a low dropout voltage regulator, which can support 10uA DC current load

- The input voltage is 2.7-3.6V (typical: 3.3V)

- Its output voltage range is 0.9V-1.42 V-2.1V

- The reference voltage and bias current are 0.6V and 0.5uA from BGR, respectively.

-

LDO regulator on SMIC 40nm, up to 12mA

- The present IP is a low-dropout (LDO) voltage regulator supporting a 12mA load current with an input voltage range of 2.7V to 3.6V (typical: 3.3V)

- It features three selectable output voltages: 0.9V, 1.1V, and 1.3V

- The reference voltage and bias current, derived from an integrated bandgap reference (BGR), are 0.6V and 0.5μA, respectively.

-

Capless LDO regulator on SMIC 65nm

- The present IP is a low-dropout (LDO) and capacitor-less voltage regulator developed using SMIC's 65nm ETOX Nor Flash process

- It generates adjustable voltages from 0.5V to 4.0V in 0.1V step with a ripple voltage of less than 80mV.

-

SMIC 0.18µm 5v-3.3v/1.8v Power Regulator

- Process: SMIC 0.18μm 3.3V/1.8V 1P5M/6M Logic process

- (This IP can work in both generic 0.18um process & 0.153um shrink process without any design change.)

- Input voltage: 2.7~5.5V

- Regulated output voltage: 3.3V±8% (in regulation region); 1.8V±8%

-

SMIC 65nm LL 3.3V-2.5/1.2V Power Regulator

- Process: SMIC 65nm 1.2V/2.5V

- Input voltage: 2.25~3.6V

- Regulated output voltage: VOUT25=2.5V±10% & VOUT12=1.2V±10%

- Dropout voltage: VOUT25(DROP)= 150mV (when IOUT25=60mA, AVDD=2.25V)