Frac-N PLL IP for Samsung

Welcome to the ultimate

Frac-N PLL IP

for

Samsung

hub! Explore our vast directory of

Frac-N PLL IP

for

Samsung

All offers in

Frac-N PLL IP

for

Samsung

Filter

Compare

15

Frac-N PLL IP

for

Samsung

from

3

vendors

(1

-

10)

-

All Digital Fractional-N RF Frequency Synthesizer PLL in Samsung 14LPP

- Ultra-low jitter, less than 300fs RMS integrated between 12kHz to 20MHz.

- Suitable for many RF applications, including LO, clocks for, ADC, DAC, high-speed PHY

- Small die area (< 0.05 sq mm), using a LC tank oscillator

- Output frequency can be from 1 to 2047 times the input reference, up to 8GHz

-

All Digital Fractional-N RF Frequency Synthesizer PLL in Samsung 8LPP

- Fractional Multiplication with frequencies up to 8GHz

- Extremely low jitter (< 300fs RMS)

- Small size (< 0.05 sq mm)

- Low Power (< 7mW)

-

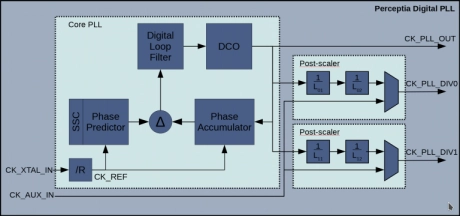

All Digital Fractional-N PLL for Performance Computing in Samsung 8LPP

- Fractional multiplication with frequency up to 4GHz

- Low jitter (< 10ps RMS)

- Small size (< 0.01 sq mm)

- Low Power (< 5mW)

- Support for multi-PLL systems

-

All Digital Fractional-N PLL for Performance Computing in Samsung 14LPP

- Fractional multiplication with frequency up to 4GHz

- Low jitter (< 10ps RMS)

- Small size (< 0.01 sq mm)

- Low Power (< 5mW)

- Support for multi-PLL systems

-

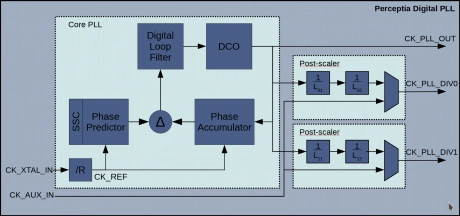

General Purpose All Digital Fractional-N PLL in Samsung 14LPP

- Low jitter (< 18ps RMS)

- Small size (< 0.01 sq mm)

- Low Power (< 3.5mW)

- Support for multi-PLL systems

-

General Purpose All Digital Fractional-N PLL in Samsung 8LPP

- Low jitter (< 18ps RMS)

- Small size (< 0.01 sq mm)

- Low Power (< 3.5mW)

- Support for multi-PLL systems

-

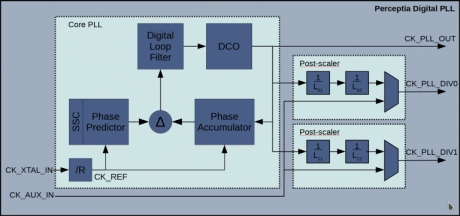

Low Power All Digital Fractional-N PLL in Samsung 14LPP

- Low power, suitable for IoT applications

- Good jitter, suitable for clocking digital logic.

- Extremely small die area (< 0.005 sq mm), using a ring oscillator

- Output frequency can be from 1 to 400 times the input reference, up to 1.5GHz

- Reference clock from 5MHz to 200MHz

-

Low Power All Digital Fractional-N PLL in GlobalFoundries 12LPP/14LPP

- Low power, suitable for IoT applications

- Good jitter, suitable for clocking digital logic.

- Extremely small die area (< 0.005 sq mm), using a ring oscillator

- Output frequency can be from 1 to 400 times the input reference, up to 1.5GHz

- Reference clock from 5MHz to 200MHz

-

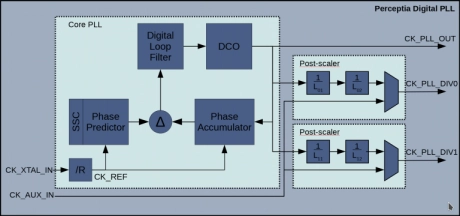

Low Power All Digital Fractional-N PLL in GlobalFoundries 22FDX

- Low power, suitable for IoT applications

- Good jitter, suitable for clocking digital logic.

- Extremely small die area (< 0.01 sq mm), using a ring oscillator

- Output frequency can be from 1 to 200 times the input reference, up to 1.0GHz

-

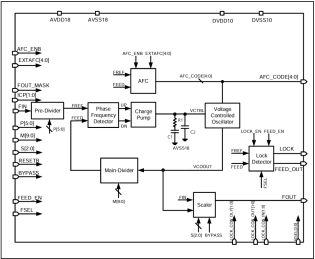

Integer PLL on Samsung 28nm LN28FDS

- PLL2851X is a 1.8V/1.0V dual supply-voltage phase locked loop (PLL) with a wide-output-frequency-range for frequency synthesis.

- It consists of a phase frequency detector (PFD), a charge pump, a voltage-controlled oscillator (VCO), a 6-bit pre divider, a 10-bit main-divider, a 3-bit scaler, a lock detector and an automatic frequency control (AFC). The maximum output frequency of PLL is 2.5GHz.