Memory & Libraries IP for GLOBALFOUNDRIES

Welcome to the ultimate

Memory & Libraries IP

for

GLOBALFOUNDRIES

hub! Explore our vast directory of

Memory & Libraries IP

for

GLOBALFOUNDRIES

All offers in

Memory & Libraries IP

for

GLOBALFOUNDRIES

Filter

Compare

107

Memory & Libraries IP

for

GLOBALFOUNDRIES

from

20

vendors

(1

-

10)

-

Stand-Alone ESD Cell in GF 28nm

- This ESD library is a silicon-proven set of discrete, pad-independent ESD clamps for GlobalFoundries 28nm technology.

- The library is designed to provide robust ESD protection for power domains and low-speed signals in advanced SoCs where traditional pad-based protection is insufficient or impractical.

-

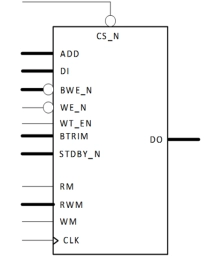

Single Port High-Speed Multi Bank SRAM Memory Compiler on GF 22FDX+

- Ultra-Low Leakage - GLOBALFOUNDRIES low-leakage 6T L110 bit cells with High Vt and low leakage periphery to ensure minimal leakage and high yield.

- Multi-Bank Architecture - Memory split into 1 to 4 banks for reduced bit line length and enhanced timing.

- Ultra Low Power Standby - Built-in source biasing trims standby current to a minimum for data retention.

-

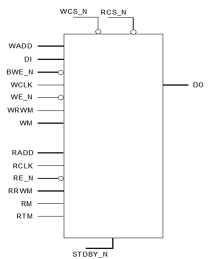

Dual Port Register File Compiler (1 Read-only port, 1 Write-only port) - GF 22FDX+

- Uses 8T-TP185SL bit cells.

- Isolated Supplies: Periphery and array power domains can be independently powered down in standby mode.

- Deep Sleep Standby Mode: Memory retains data at minimal power via internal biasing.

-

Single Port Low Leakage SRAM Memory Compiler on GF 22FDX+

- Ultra-Low Leakage: High VT (HVT) and low leakage (LLHVT) devices are used with source biasing to minimize standby currents while operating at low voltage

- Bit Cell: Utilizes GlobalFoundries® Ultra-Low Leakage 6T (P110UL) bit cells to ensure high manufacturing yields

- Five Power Modes: High Performance, Low Leakage, Standby, Retention, and Power Off modes provide flexibility for power optimization

- Speed Grades: Three options to adjust the speed/leakage balance and optimize for high speed or low power operation

-

Single Port Low Leakage Register File Compiler - GF 22FDX+

- Ultra-Low Leakage: High VT (HVT) and low leakage HVT (LLHVT) devices used with source biasing to minimize standby currents while operating at low voltage.

- Bit Cell: Utilizes GlobalFoundries® Ultra-Low Leakage 6T (L110) bit cells to ensure high manufacturing yields.

- Four Power Modes: Active, Standby, Retention, and Power Off modes provide flexibility for power optimization

-

Single Port Low Leakage SRAM Memory Compiler on GF 22FDX

- Ultra-Low Leakage: High VT (HVT) and low leakage (LLHVT) devices are used with source biasing to minimize standby currents while operating at low voltage

- Bit Cell: Utilizes GlobalFoundries® Ultra-Low Leakage 6T (P110UL) bit cells to ensure high manufacturing yields

- Five Power Modes: High Performance, Low Leakage, Standby, Retention, and Power Off modes provide flexibility for power optimization

- Speed Grades: Three options to adjust the speed/leakage balance and optimize for high speed or low power operation

-

Single Port Low Leakage Register File Compiler - GF 22FDX+

- Ultra-Low Leakage: High VT (HVT) and low leakage HVT (LLHVT) devices used with source biasing to minimize standby currents while operating at low voltage

- Bit Cell: Utilizes GlobalFoundries® Ultra-Low Leakage 6T (P110UL) bit cells to ensure high manufacturing yields

- Four Power Modes: Active, Standby, Retention, and Power Off modes provide flexibility for power optimization

-

Single Port Low Leakage SRAM Memory Compiler on GF 22FDX+

- Ultra-Low Leakage: High VT (HVT) and low leakage (LLHVT) devices are used with source biasing to minimize standby currents while operating at low voltage

- Bit Cell: Utilizes GlobalFoundries® Ultra-Low Leakage, 6T(L110) bit cells to ensure high manufacturing yields

- Five Power Modes: High Performance, Low Leakage, Standby, Retention, and Power Off modes provide flexibility for power optimization

-

Single Port Low Leakage Register File Compiler - GF 22FDX

- Ultra-Low Leakage: High VT (HVT) and low leakage HVT (LLHVT) devices used with source biasing to minimize standby currents while operating at low voltage

- Bit Cell: Utilizes GlobalFoundries® Ultra-Low Leakage 6T (P110UL) bit cells to ensure high manufacturing yields

- Four Power Modes: Active, Standby, Retention, and Power Off modes provide flexibility for power optimization

-

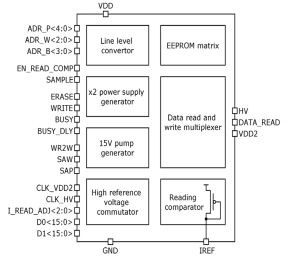

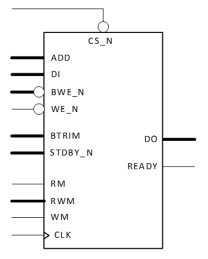

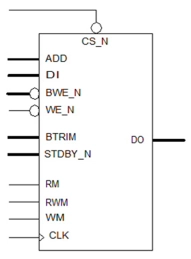

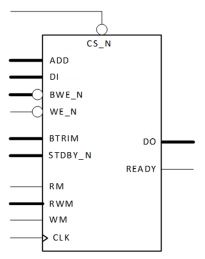

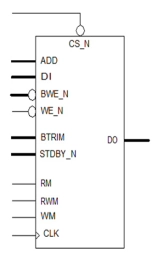

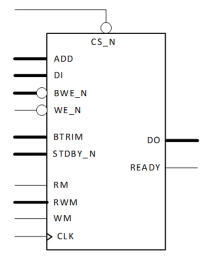

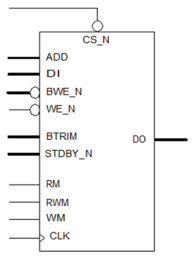

3.6Kbit EEPROM IP with configuration 28p8w16bit

- 130GF_EEPROM_08 IP is a nonvolatile electrically erasable programmable read-only memory (EEPROM) with volume 3.6 Kbits, which is organized as 28 pages of 8 words by 16 bit with single-bit output data and parallel write data.

- Data programming in EEPROM consists of 2 consecutive phases - erasing and writing.